Section 2 CPU

Rev. 7.00 Mar 10, 2005 page 57 of 652

REJ09B0042-0700

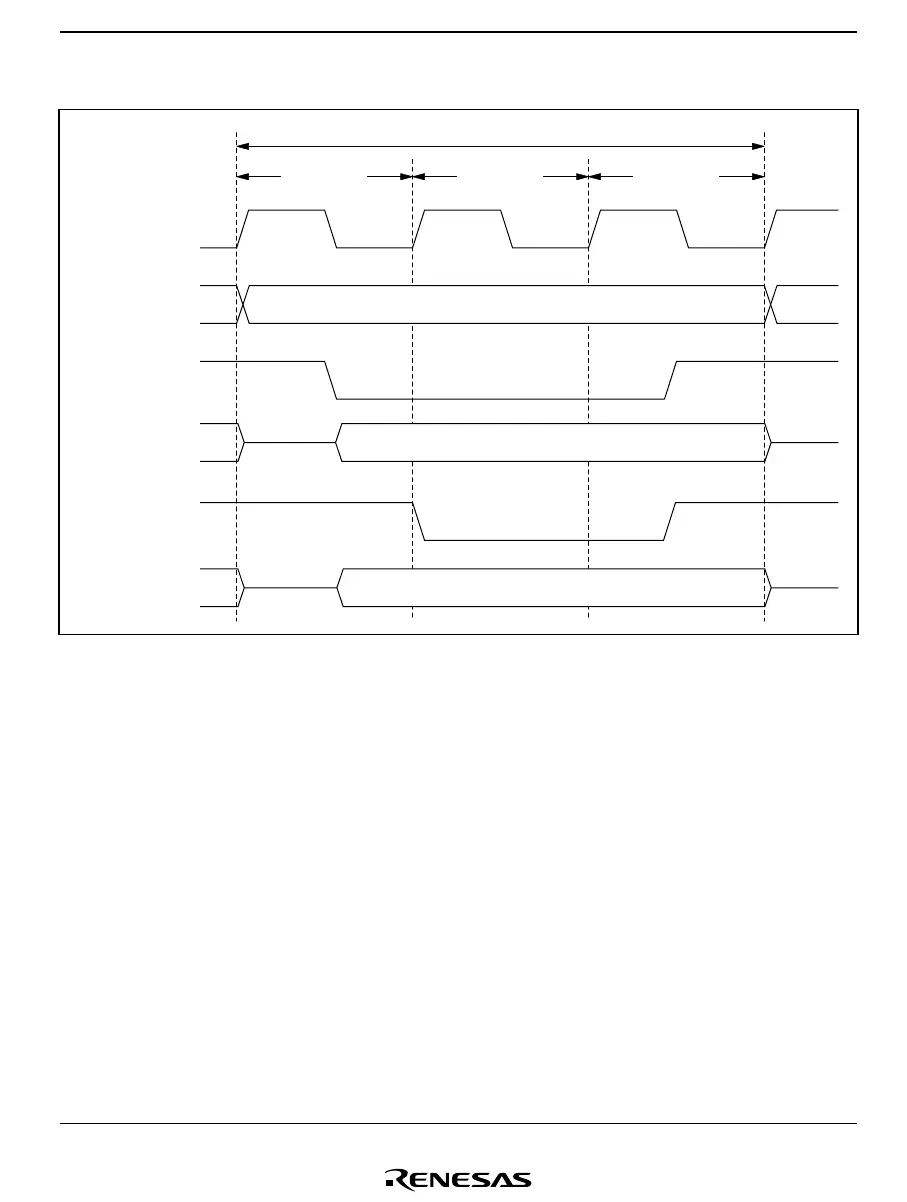

Three-state access to on-chip peripheral modules

T

1

state

Bus cycle

Internal

address bus

Internal

read signal

Internal

data bus

(read access)

Internal

write signal

Read data

Address

Internal

data bus

(write access)

T

2

state T

3

state

Write data

φ or φ

SUB

Figure 2.13 On-Chip Peripheral Module Access Cycle (3-State Access)

2.7 CPU States

2.7.1 Overview

There are four CPU states: the reset state, program execution state, program halt state, and

exception-handling state. The program execution state includes active (high-speed or medium-

speed) mode and subactive mode. In the program halt state there are a sleep (high-speed or

medium-speed) mode, standby mode, watch mode, and sub-sleep mode. These states are shown in

figure 2.14. Figure 2.15 shows the state transitions.

Loading...

Loading...