Section 9 Timers

Rev. 7.00 Mar 10, 2005 page 264 of 652

REJ09B0042-0700

9.4.2 Register Descriptions

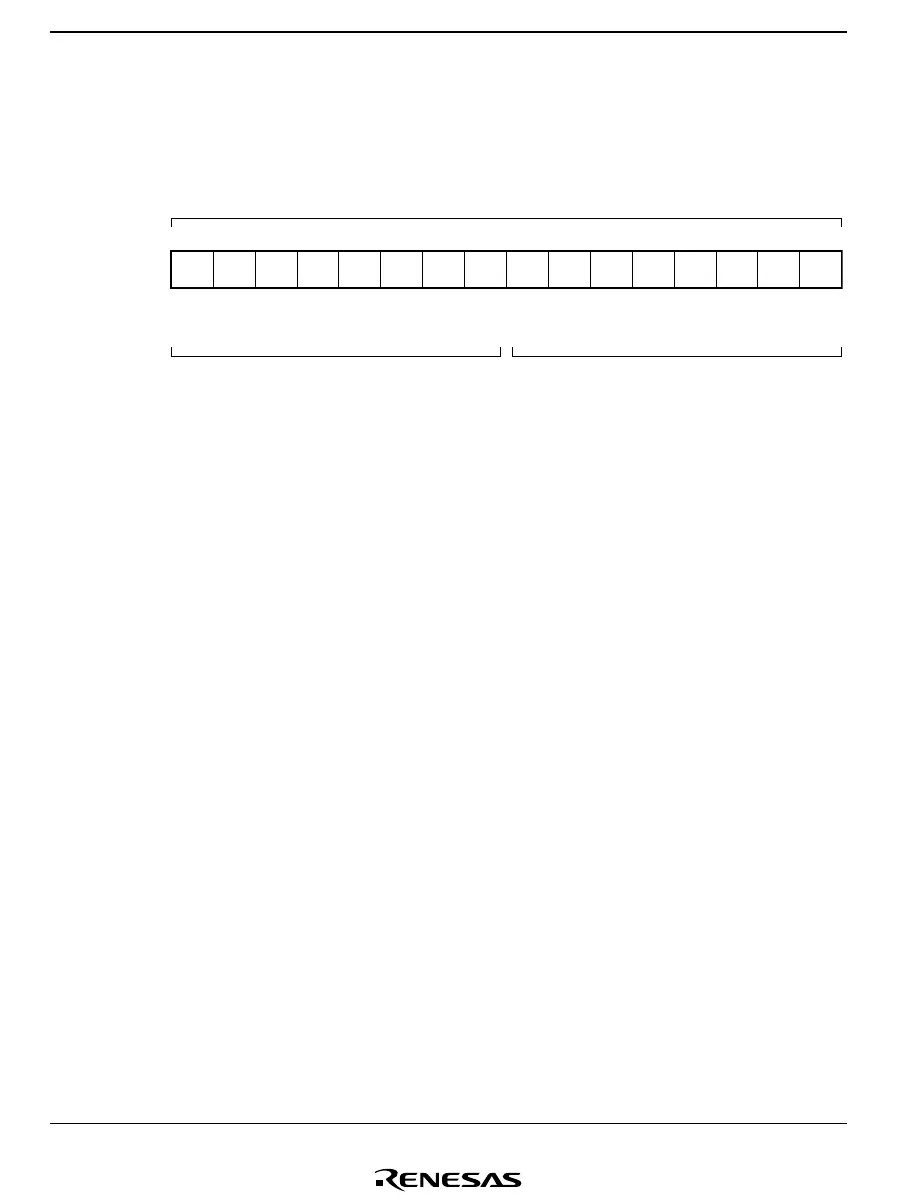

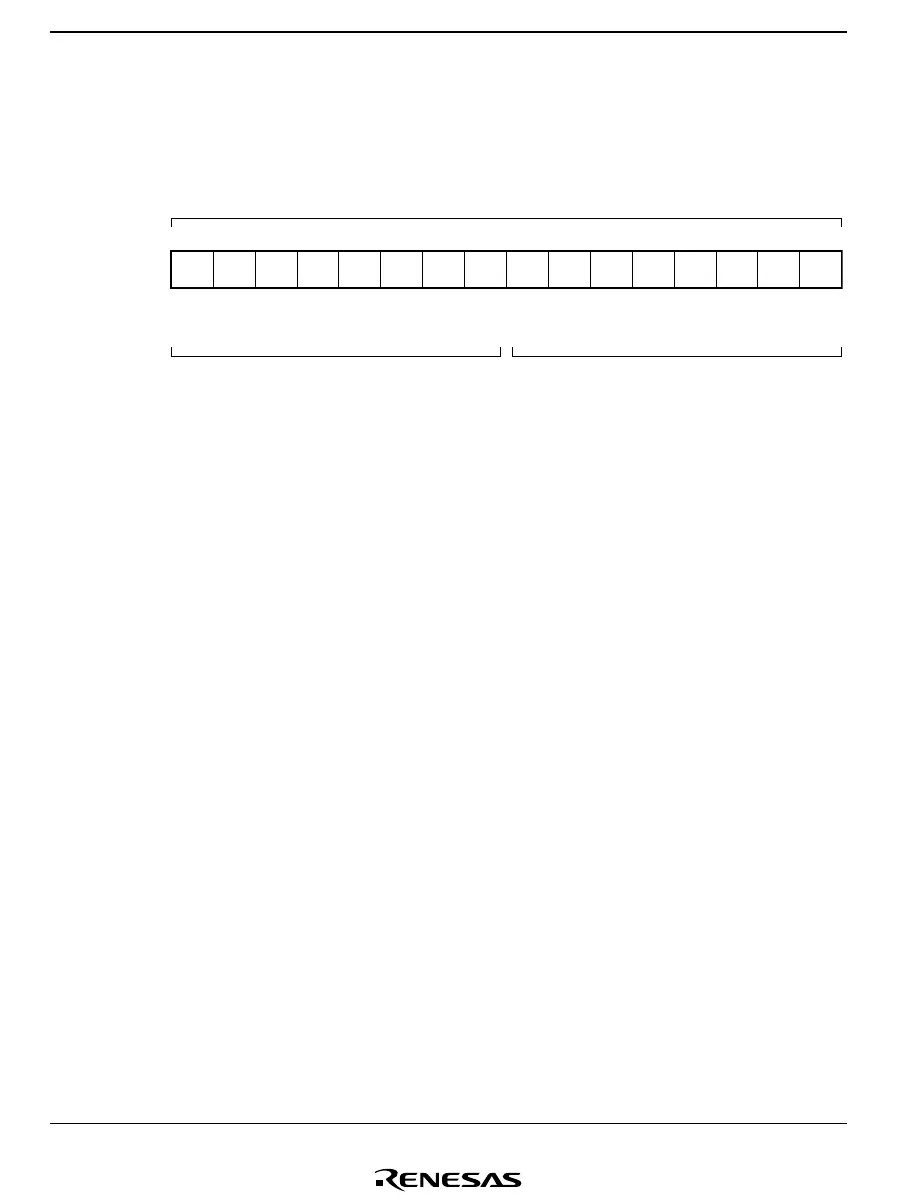

16-bit Timer Counter (TCF)

8-bit Timer Counter (TCFH)

8-bit Timer Counter (TCFL)

15 14 13 12 11 10 9 8

TCF

TCFH TCFL

76543210

0000000000000000

R/W

Bit:

Initial value:

Read/Write: R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

TCF is a 16-bit read/write up-counter configured by cascaded connection of 8-bit timer counters

TCFH and TCFL. In addition to the use of TCF as a 16-bit counter with TCFH as the upper 8 bits

and TCFL as the lower 8 bits, TCFH and TCFL can also be used as independent 8-bit counters.

TCFH and TCFL can be read and written by the CPU, but when they are used in 16-bit mode, data

transfer to and from the CPU is performed via a temporary register (TEMP). For details of TEMP,

see section 9.4.3, CPU Interface.

TCFH and TCFL are each initialized to H'00 upon reset.

a. 16-bit mode (TCF)

When CKSH2 is cleared to 0 in TCRF, TCF operates as a 16-bit counter. The TCF input clock

is selected by bits CKSL2 to CKSL0 in TCRF.

TCF can be cleared in the event of a compare match by means of CCLRH in TCSRF.

When TCF overflows from H'FFFF to H'0000, OVFH is set to 1 in TCSRF. If OVIEH in

TCSRF is 1 at this time, IRRTFH is set to 1 in IRR2, and if IENTFH in IENR2 is 1, an

interrupt request is sent to the CPU.

b. 8-bit mode (TCFL/TCFH)

When CKSH2 is set to 1 in TCRF, TCFH, and TCFL operate as two independent 8-bit

counters. The TCFH (TCFL) input clock is selected by bits CKSH2 to CKSH0 (CKSL2 to

CKSL0) in TCRF.

TCFH (TCFL) can be cleared in the event of a compare match by means of CCLRH (CCLRL)

in TCSRF.

When TCFH (TCFL) overflows from H'FF to H'00, OVFH (OVFL) is set to 1 in TCSRF. If

OVIEH (OVIEL) in TCSRF is 1 at this time, IRRTFH (IRRTFL) is set to 1 in IRR2, and if

IENTFH (IENTFL) in IENR2 is 1, an interrupt request is sent to the CPU.

Loading...

Loading...