Section 2 CPU

Rev. 7.00 Mar 10, 2005 page 56 of 652

REJ09B0042-0700

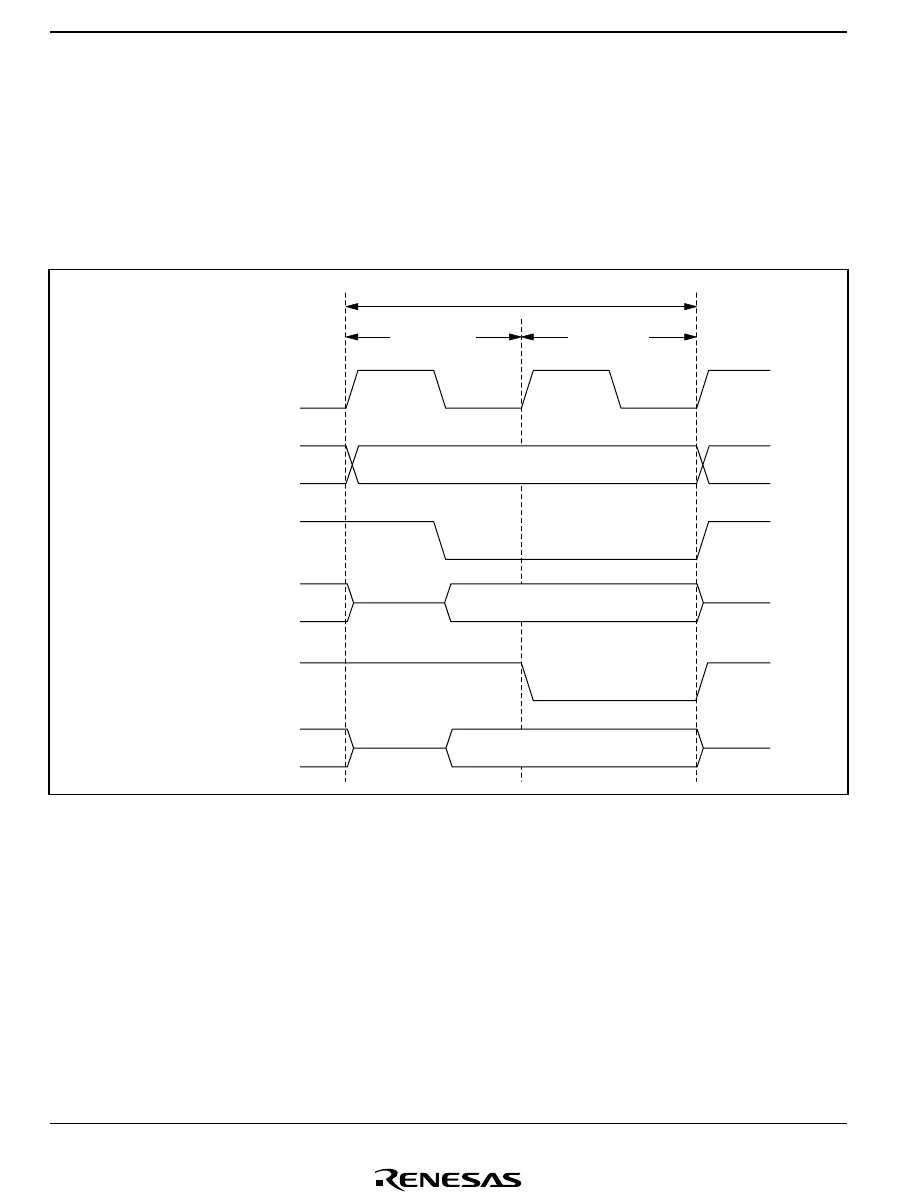

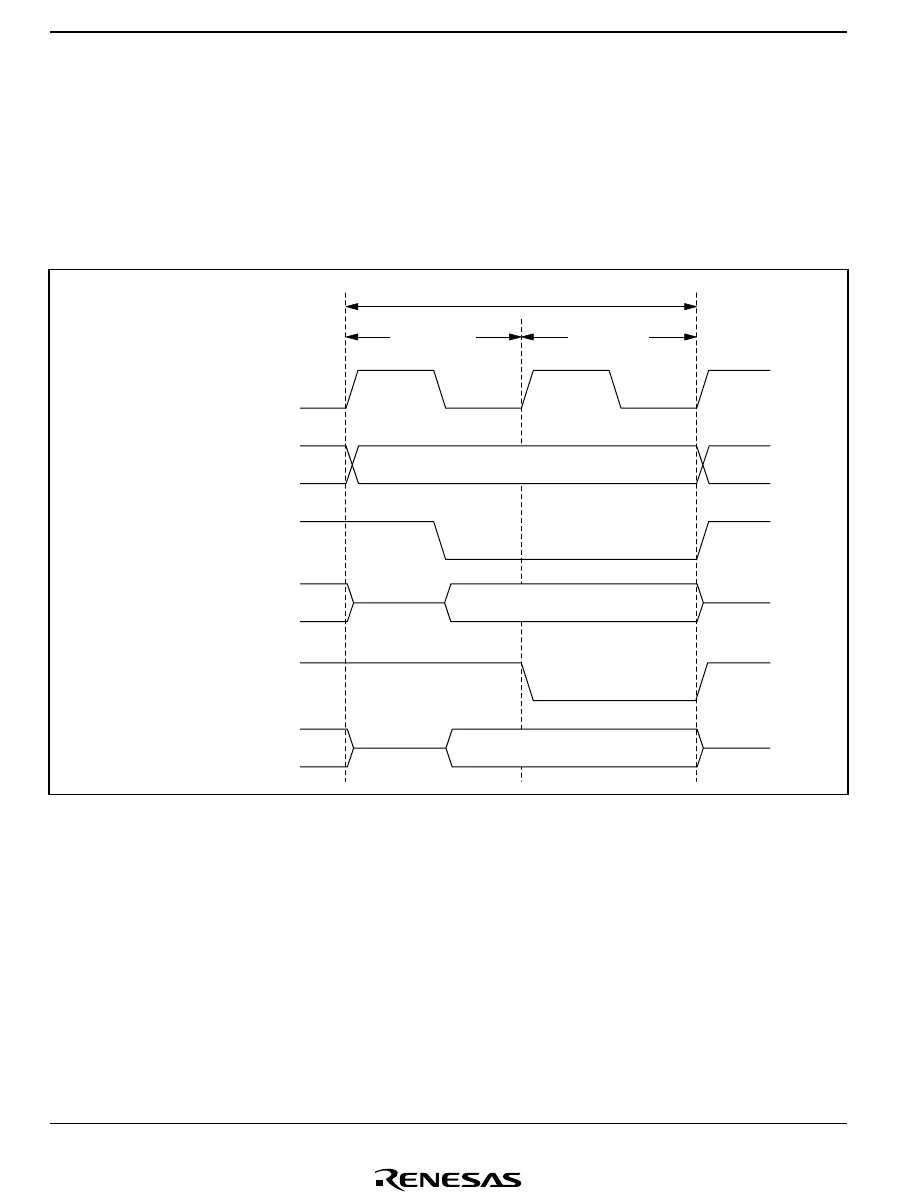

2.6.2 Access to On-Chip Peripheral Modules

On-chip peripheral modules are accessed in two states or three states. The data bus width is 8 bits,

so access is by byte size only. This means that for accessing word data, two instructions must be

used. Figures 2.12 and 2.13 show the on-chip peripheral module access cycle.

Two-state access to on-chip peripheral modules

T

1

state

Bus cycle

T

2

state

φ or φ

SUB

Internal address bus

Internal read signal

Internal data bus

(read access)

Internal write signal

Read data

Address

Write data

Internal data bus

(write access)

Figure 2.12 On-Chip Peripheral Module Access Cycle (2-State Access)

Loading...

Loading...