Section 9 Timers

Rev. 7.00 Mar 10, 2005 page 302 of 652

REJ09B0042-0700

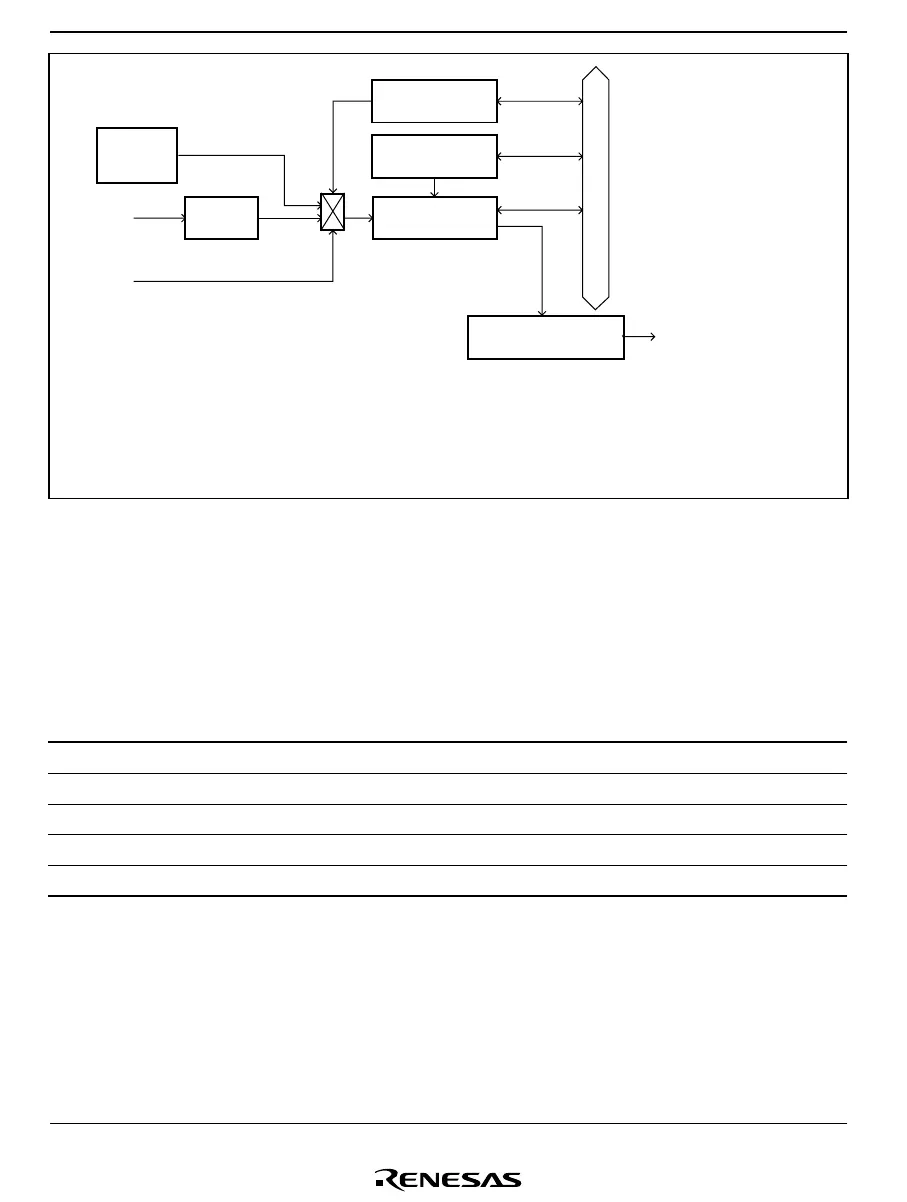

TCSRW

TMW

TCW

Internal data bus

PSS

Watchdog

on-chip

oscillator

φ

φ

W

/32

Internal reset signal or

interrupt request signal

Interrupt/reset

controller

[Legend]

TCSRW:

TCW:

TMW:

PSS:

Timer control/status register W

Timer counter W

Timer mode register W

Prescaler S

Figure 9.17(2) Block Diagram of Watchdog Timer

(H8/38124 Group)

Register Configuration

Table 9.16 shows the register configuration of the watchdog timer.

Table 9.16 Watchdog Timer Registers

Name Abbr. R/W Initial Value Address

Timer control/status register W TCSRW R/W H'AA H'FFB2

Timer counter W TCW R/W H'00 H'FFB3

Timer mode register W

*

TMW R/W H'FF H'FFF8

Clock stop register 2 CKSTPR2 R/W H'FF H'FFFB

Port mode register 2 PMR2 R/W H'D8 H'FFC9

Note: * This register is implemented on the H8/38124 Group only.

Loading...

Loading...