Section 1 Overview

Rev. 7.00 Mar 10, 2005 page 8 of 652

REJ09B0042-0700

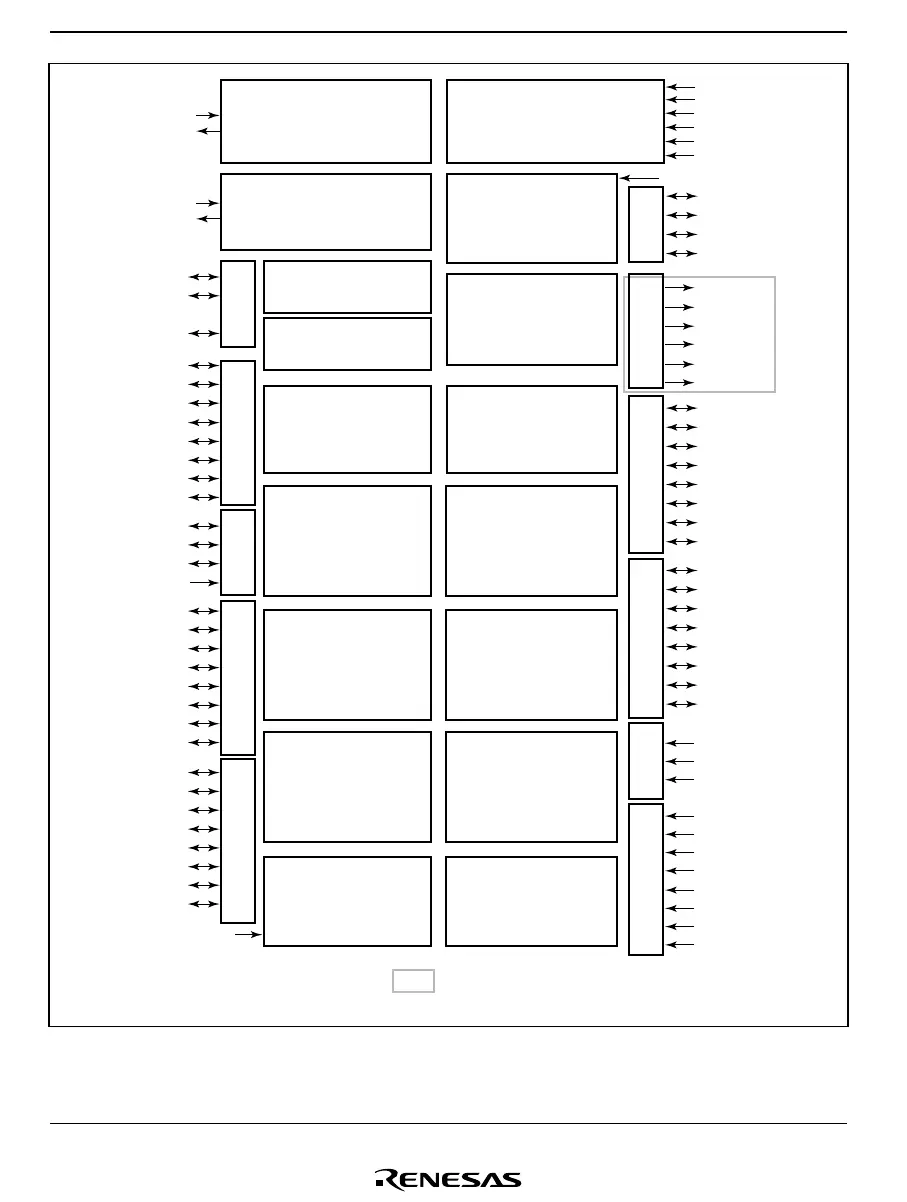

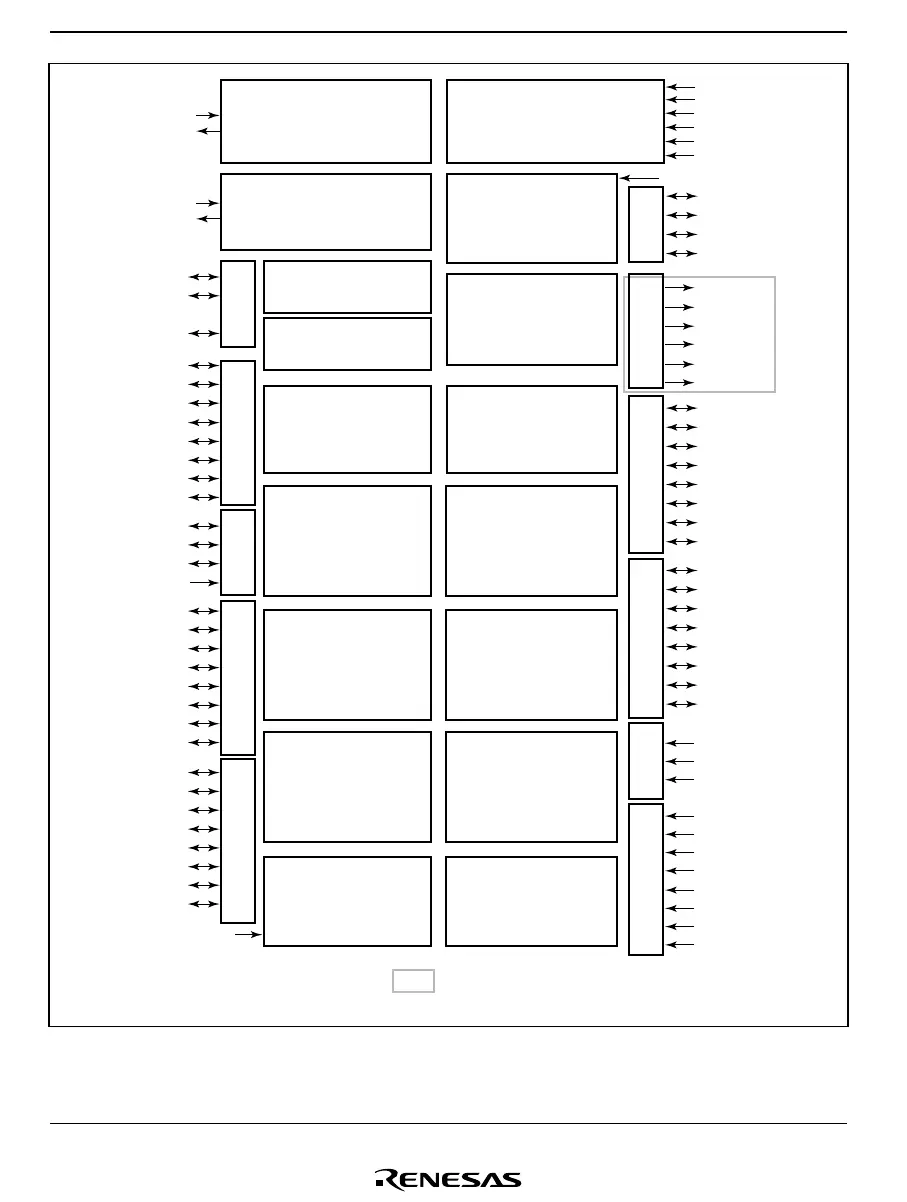

Sub clock

OSC

H8/300L

CPU

RAM

(512 bytes to 1 Kbyte)

System clock

OSC

ROM

(8 Kbytes to 32 Kbytes)

Power-on reset and

low-voltage detect circuits

Timer A

Timer C

Timer F

Timer G

Asynchronous

counter

(16 bits)

A/D

(10 bits)

Serial

communication

interface

(SCI3)

10-bit PWM1

10-bit PWM2

LCD

controller

Large-current (15 mA/pin)

PA

3

/COM

4

PA

2

/COM

3

PA

1

/COM

2

PA

0

/COM

1

P7

7

/SEG

24

P7

6

/SEG

23

P7

5

/SEG

22

P7

4

/SEG

21

P7

3

/SEG

20

P7

2

/SEG

19

P7

1

/SEG

18

P7

0

/SEG

17

P8

7

/SEG

32

P8

6

/SEG

31

P8

5

/SEG

30

P8

4

/SEG

29

P8

3

/SEG

28

P8

2

/SEG

27

P8

1

/SEG

26

P8

0

/SEG

25

P6

0

/SEG

9

P6

1

/SEG

10

P6

2

/SEG

11

P6

3

/SEG

12

P6

4

/SEG

13

P6

5

/SEG

14

P6

6

/SEG

15

P6

7

/SEG

16

P4

0

/SCK

32

P4

1

/RXD

32

P4

2

/TXD

32

P4

3

/IRQ

0

OSC

1

OSC

2

x

1

x

2

P1

3

/TMIG

P1

4

/IRQ

4

/ADTRG

P1

7

/IRQ

3

/TMIF

P3

0

/UD

P3

1

/TMOFL

P3

2

/TMOFH

P3

3

P3

4

P3

5

P3

6

/AEVH

P3

7

/AEVL

P5

0

/WKP

0

/SEG

1

P5

1

/WKP

1

/SEG

2

P5

2

/WKP

2

/SEG

3

P5

3

/WKP

3

/SEG

4

P5

4

/WKP

4

/SEG

5

P5

5

/WKP

5

/SEG

6

P5

6

/WKP

6

/SEG

7

P5

7

/WKP

7

/SEG

8

PB

7

/AN

7

PB

6

/AN

6

PB

5

/AN

5

PB

4

/AN

4

PB

3

/AN

3

/IRQ

1

/TMIC

PB

2

/AN

2

PB

1

/AN

1

/extU

PB

0

/AN

0

/extD

V

1

V

2

V

3

IRQAEC

P9

5

P9

4

P9

3

/V

ref

P9

2

P9

1

/PWM

2

P9

0

/PWM

1

AV

CC

WDT

CV

CC

V

SS

V

SS

= AV

SS

V

CC

RES

TEST

Note: If the on-chip emulator is used, pins 95,

33, 34, and 35 are reserved for the

emulator and not available to the user.

Port 6 Port 5 Port 4 Port 3 Port 1

Port APort 9Port 8Port 7

LCD power

supply

Port B

Figure 1.1(2) Block Diagram (H8/38124 Group)

Loading...

Loading...