Section 1 Overview

Rev. 7.00 Mar 10, 2005 page 10 of 652

REJ09B0042-0700

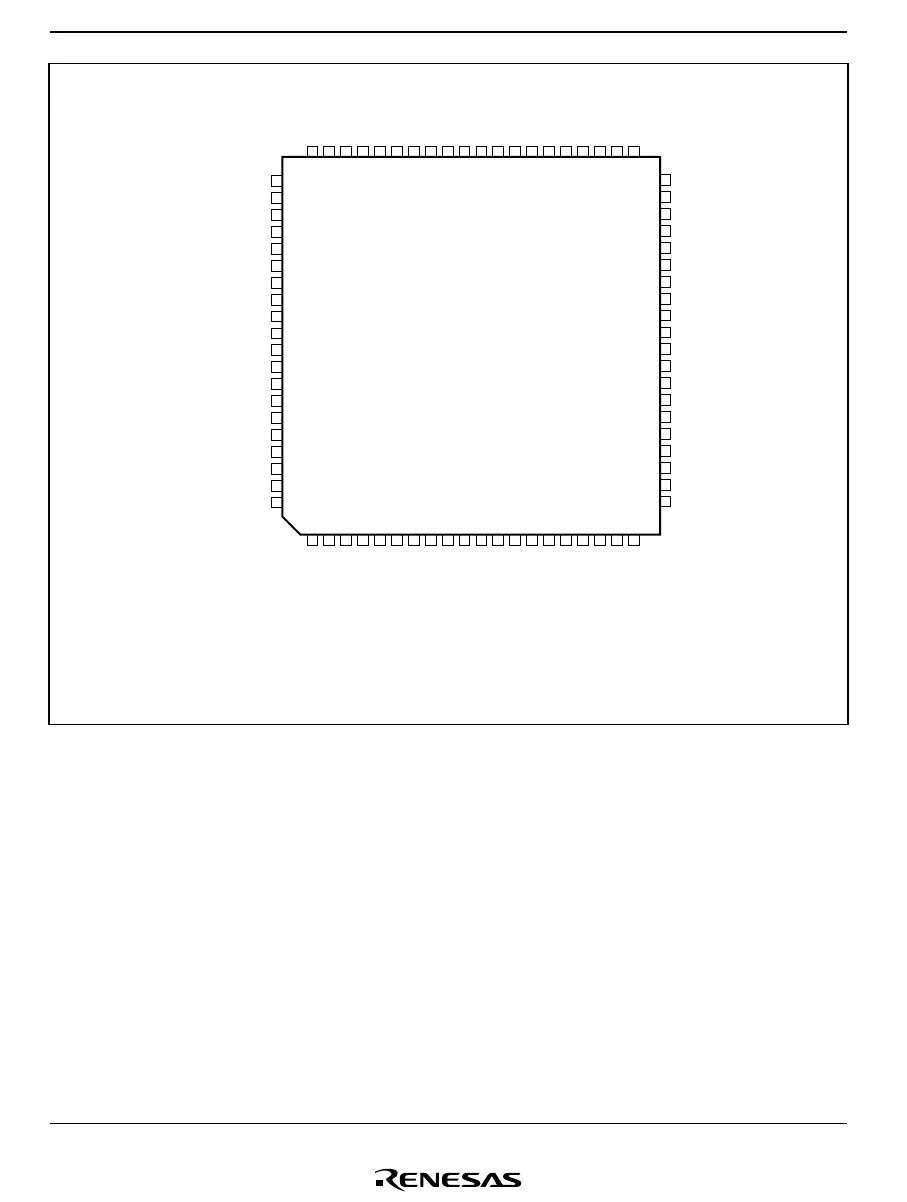

FP-80A,TFP-80C

(Top view)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

P3

0

/UD

P3

1

/TMOFL

P3

2

/TMOFH

P3

3

P3

4

P3

5

P3

6

/AEVH

P3

7

/AEVL

P4

0

/SCK

32

P4

1

/RXD

32

P4

2

/TXD

32

P4

3

/IRQ

0

PB

0

/AN

0

/extD

PB

1

/AN

1

/extU

PB

2

/AN

2

PB

3

/AN

3

/IRQ

1

/TMIC

PB

4

/AN

4

PB

5

/AN

5

PB

6

/AN

6

PB

7

/AN

7

AV

CC

P1

3

/TMIG

P1

4

/IRQ

4

/ADTRG

CV

CC

P1

7

/IRQ

3

/TMIF

X

1

X

2

V

SS

=AV

SS

OSC

2

OSC

1

TEST

RES

P5

0

/WKP

0

/SEG

1

P5

1

/WKP

1

/SEG

2

P5

2

/WKP

2

/SEG

3

P5

3

/WKP

3

/SEG

4

P5

4

/WKP

4

/SEG

5

P5

5

/WKP

5

/SEG

6

P5

6

/WKP

6

/SEG

7

P5

7

/WKP

7

/SEG

8

P8

3

/SEG

28

P8

2

/SEG

27

P8

1

/SEG

26

P8

0

/SEG

25

P7

7

/SEG

24

P7

6

/SEG

23

P7

5

/SEG

22

P7

4

/SEG

21

P7

3

/SEG

20

P7

2

/SEG

19

P7

1

/SEG

18

P7

0

/SEG

17

P6

7

/SEG

16

P6

6

/SEG

15

P6

5

/SEG

14

P6

4

/SEG

13

P6

3

/SEG

12

P6

2

/SEG

11

P6

1

/SEG

10

P6

0

/SEG

9

IRQAEC

P9

5

P9

4

P9

3

/V

ref

P9

2

P9

1

/PWM

2

P9

0

/PWM

1

V

SS

V

CC

V

1

V

2

V

3

PA

0

/COM

1

PA

1

/COM

2

PA

2

/COM

3

PA

3

/COM

4

P8

7

/SEG

32

P8

6

/SEG

31

P8

5

/SEG

30

P8

4

/SEG

29

Note: If the on-chip emulator is used, pins 95, 33, 34, and 35 are reserved for the emulator and not available to the user.

Figure 1.2(2) Pin Arrangement (FP-80A, TFP-80C: Top View, H8/38124 Group)

Loading...

Loading...