Appendix B Internal I/O Registers

Rev. 7.00 Mar 10, 2005 page 570 of 652

REJ09B0042-0700

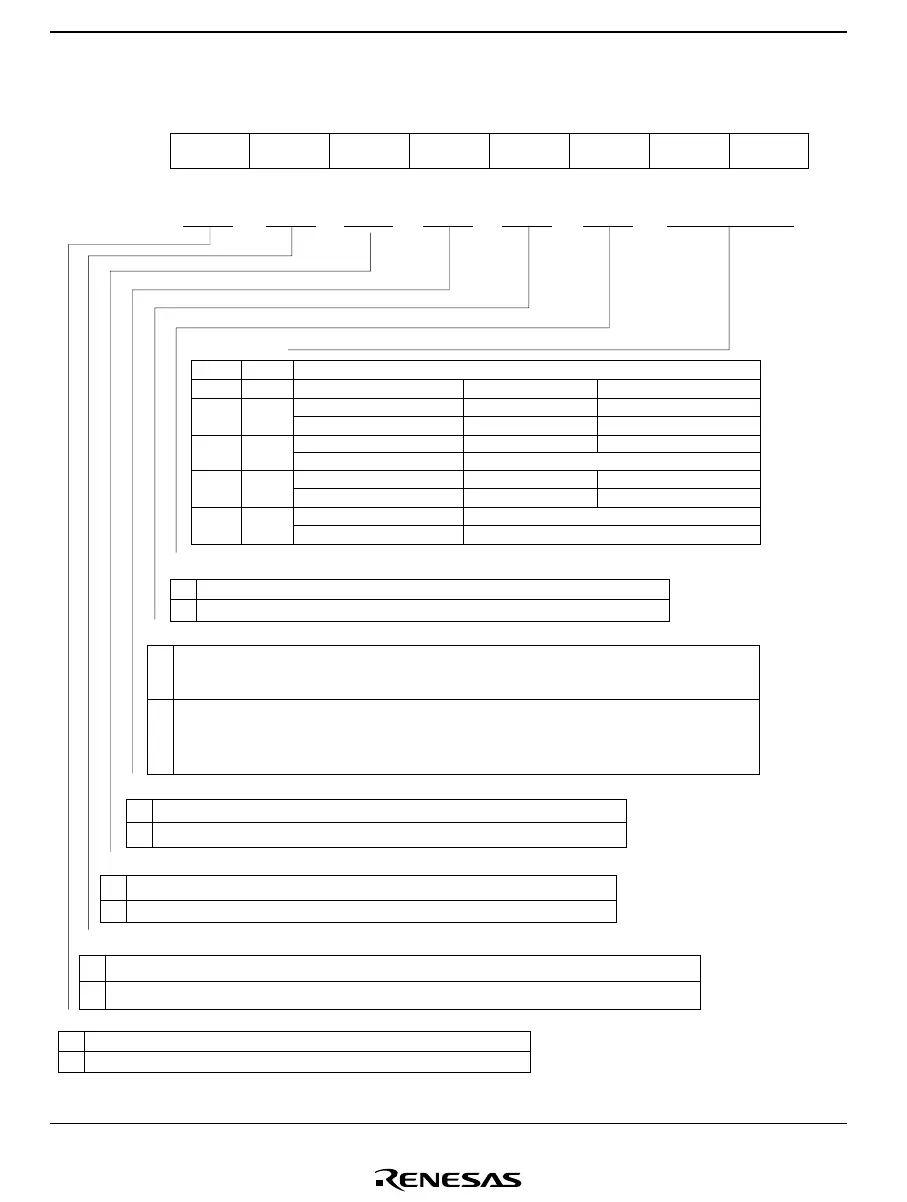

SCR3—Serial Control Register 3 H'AA SCI3

Bit

Initial value

Read/Write

7

TIE

0

R/W

6

RIE

0

R/W

5

TE

0

R/W

0

CKE0

0

R/W

2

TEIE

0

R/W

1

CKE1

0

R/W

4

RE

0

R/W

Receive Interrupt Enable

0

Receive data full interrupt request (RXI) and receive error interrupt request (ERI) disabled

1 Receive data full interrupt request (RXI) and receive error interrupt request (ERI) enabled

Multiprocessor Interrupt Enable

0

Multiprocessor interrupt request disabled (normal receive operation)

[Clearing condition]

When data is received in which the multiprocessor bit is set to 1

1 Multiprocessor interrupt request enabled

The receive interrupt request (RXI), receive error interrupt request (ERI), and setting of the

RDRF, FER, and OER flags in the serial status register (SSR), are disabled until data with

the multiprocessor bit set to 1 is received.

Transmit Enable

0

Transmit operation disabled (TXD

32

pin is I/O port)

1 Transmit operation enabled (TXD

32

pin is transmit data pin)

Receive Enable

0

Receive operation disabled (RXD

32

pin is I/O port)

1 Receive operation enabled (RXD

32

pin is receive data pin)

Transmit End Interrupt Enable

Clock Enable

0

Bit 1

CKE1

0

0

1

1

Bit 0

CKE0

0

1

0

1

Communication Mode

Asynchronous

Synchronous

Asynchronous

Synchronous

Asynchronous

Synchronous

Asynchronous

Synchronous

Internal clock

Internal clock

Internal clock

Reserved (Do not specify this combination)

External clock

External clock

Reserved (Do not specify this combination)

Reserved (Do not specify this combination)

I/O port

Serial clock output

Clock output

Clock input

Serial clock input

Clock Source SCK

32

Pin Function

Description

Transmit end interrupt request (TEI) disabled

1 Transmit end interrupt request (TEI) enabled

Transmit Interrupt Enable

0

Transmit data empty interrupt request (TXI) disabled

1 Transmit data empty interrupt request (TXI) enabled

3

MPIE

0

R/W

Loading...

Loading...