Appendix B Internal I/O Registers

Rev. 7.00 Mar 10, 2005 page 573 of 652

REJ09B0042-0700

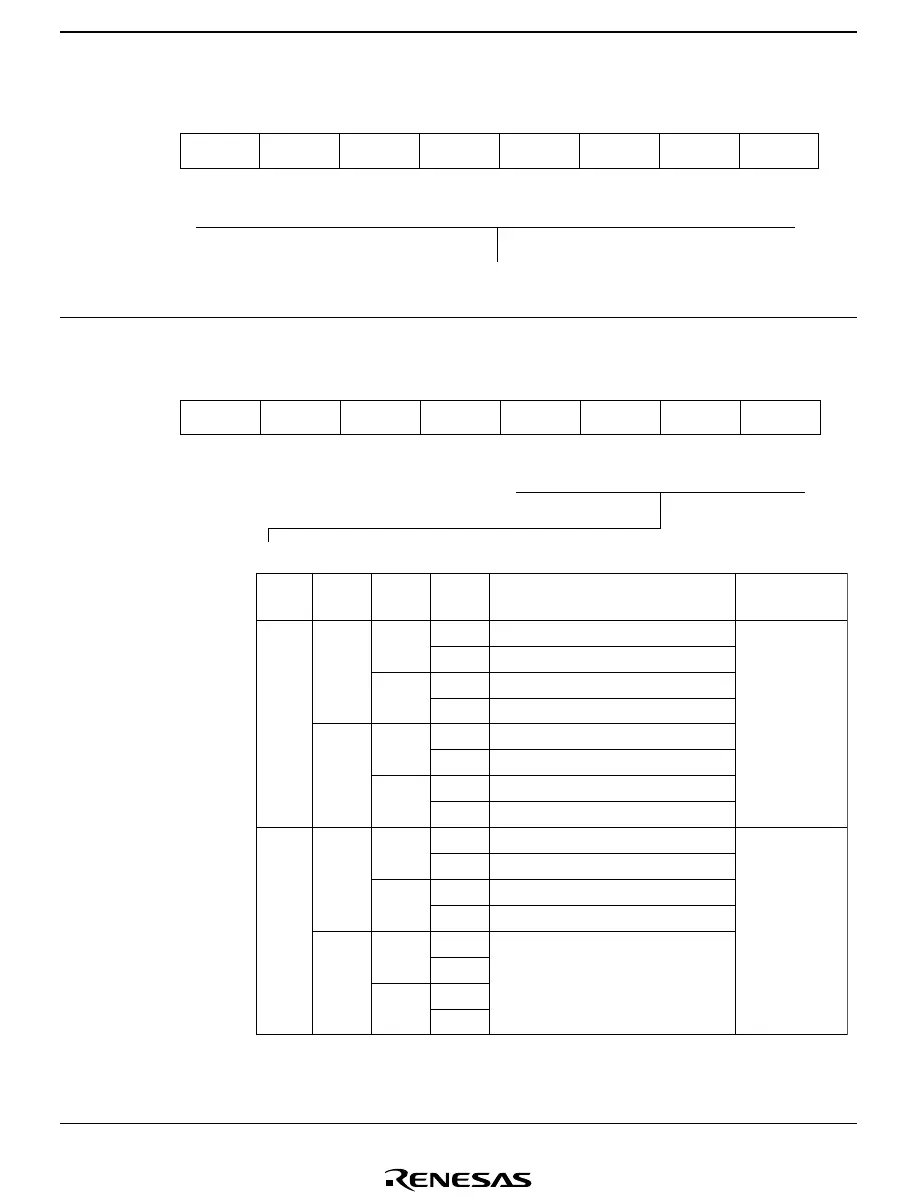

RDR—Receive Data Register H'AD SCI3

Bit

Initial value

Read/Write

7

RDR7

0

R

6

RDR6

0

R

5

RDR5

0

R

4

RDR4

0

R

3

RDR3

0

R

0

RDR0

0

R

2

RDR2

0

R

1

RDR1

0

R

Serial receiving data are stored

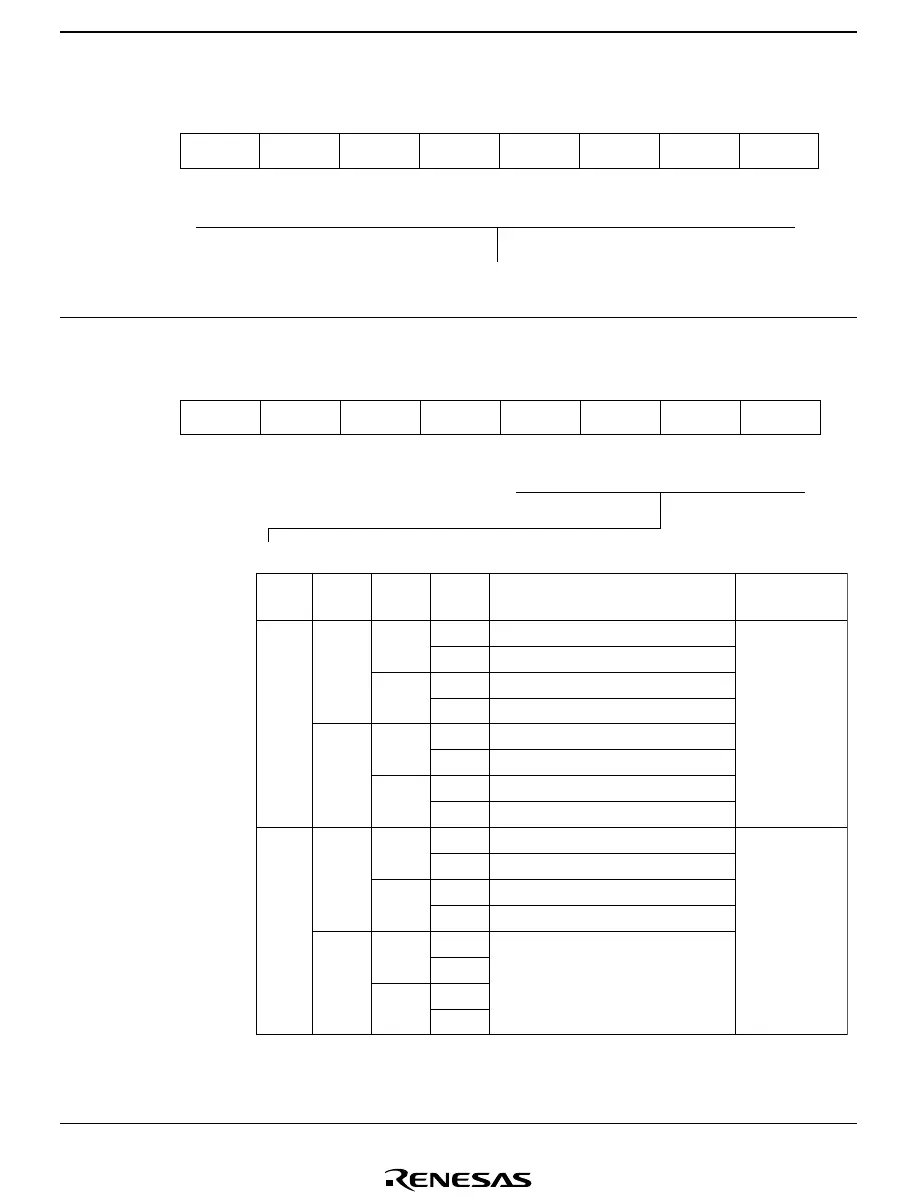

TMA—Timer Mode Register A H'B0 Timer A

Bit

Initial value

Read/Write

7

W

6

W

5

W

0

TMA0

0

R/W

2

TMA2

0

R/W

1

TMA1

0

R/W

Internal Clock Select

TMA3

TMA2

0 PSS

PSS

PSS

PSS

0

4

1

TMA1

0

1

TMA0

0

0

1

1

PSS

PSS

PSS

PSS

10

1

0

0

1

1

1 PSW

PSW

PSW

PSW

00

1

0

0

1

1

PSW and TCA are reset

10

1

0

0

1

1

Prescaler and Divider Ratio

or Overflow Period

φ/8192

φ/4096

φ/2048

φ/512

φ/256

φ/128

φ/32

φ/8

1 s

0.5 s

0.25 s

0.03125 s

Interval

timer

Clock time

base

(when

using

32.768 kHz)

Function

3

TMA3

0

R/W

Loading...

Loading...