Section 2 CPU

Rev. 7.00 Mar 10, 2005 page 35 of 652

REJ09B0042-0700

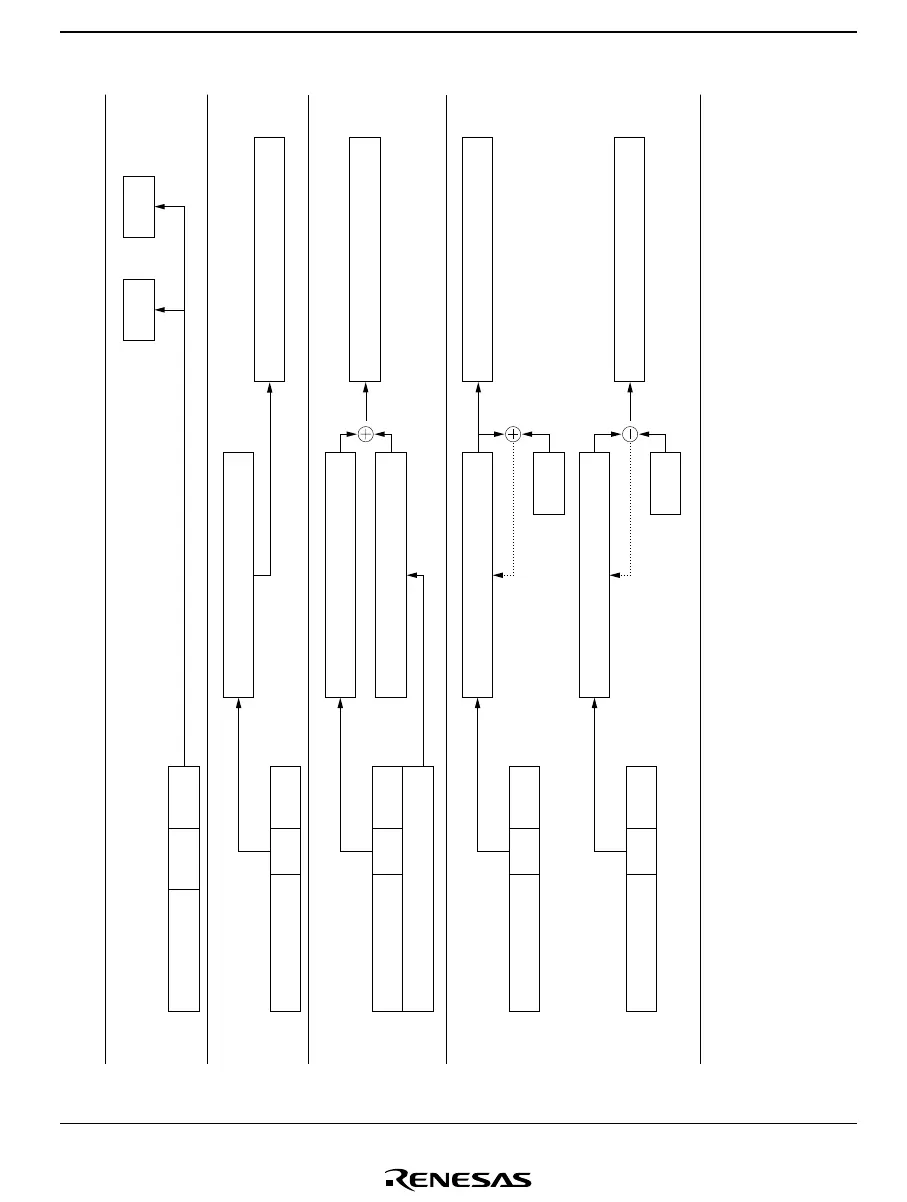

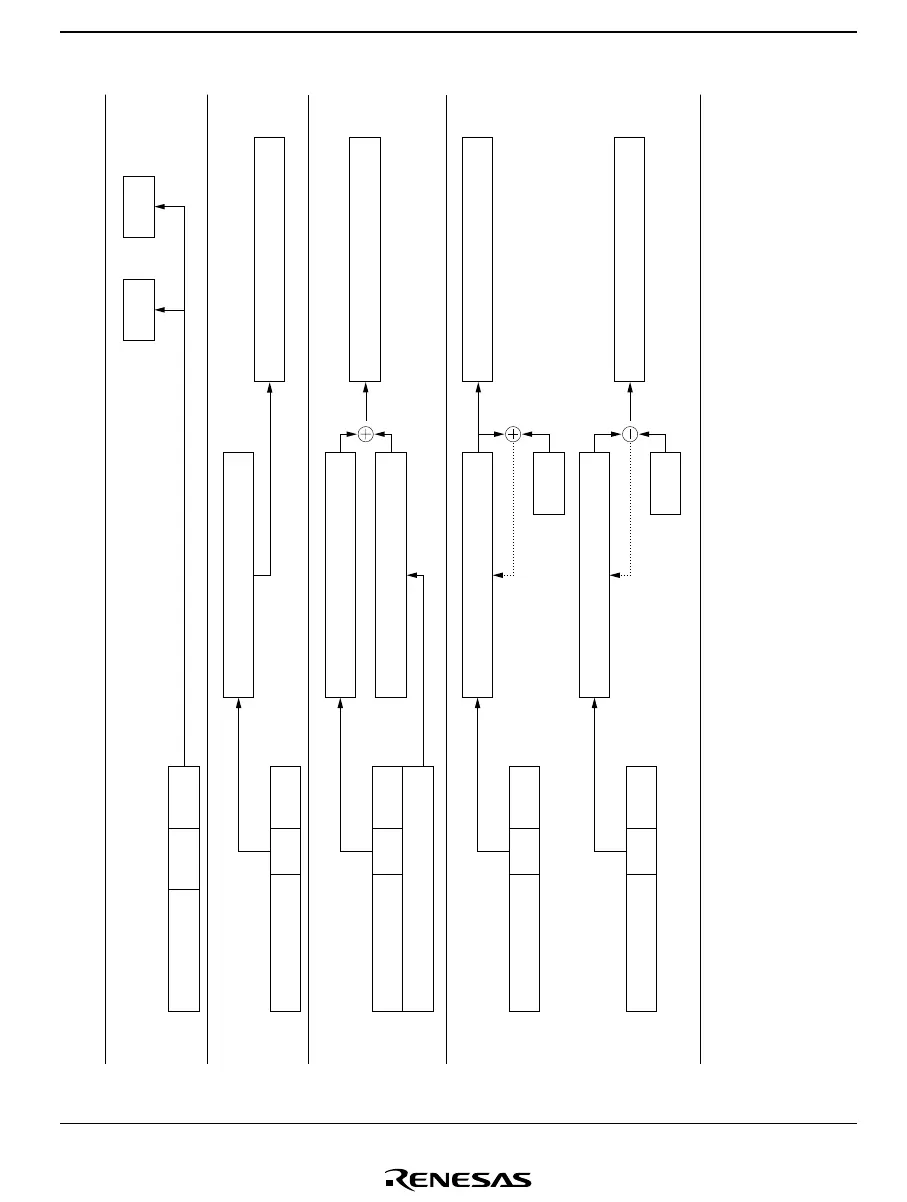

Table 2.2 Effective Address Calculation

Addressing Mode and

Instruction Format

op rm

76 34015

No. Effective Address Calculation Method Effective Address (EA)

1 Register direct, Rn

Operand is contents of registers indicated by rm/rn

Register indirect, @Rn

Contents (16 bits) of register

indicated by rm

015

Register indirect with displacement,

@(d:16, Rn)

op rm rn

87 34015

op rm

76 34015

disp

op rm

76 34015

Register indirect with

post-increment, @Rn+

op rm

76 34015

Register indirect with pre-decrement,

@−Rn

2

3

4

Incremented or decremented

by 1 if operand is byte size,

and by 2 if word size

015

disp

015

015

015

1 or 2

015

015

1 or 2

015

rm

30

rn

30

Contents (16 bits) of register

indicated by rm

Contents (16 bits) of register

indicated by rm

Contents (16 bits) of register

indicated by rm

Loading...

Loading...