127

Normal ON/OFF/falling or

rising pulse edge

2) Operands

The increase or decrease data address

16 bits / 32 bits/64 bits,BIN

3) Suitable soft components

*Notes: D includes D, HD; TD includes TD, HTD; CD includes CD, HCD, HSCD, HSD; DM

includes DM, DHM; DS includes DS, DHS. M includes M,HM,SM;S includes S,HS;T

includes T,HT;C includes C, HC.

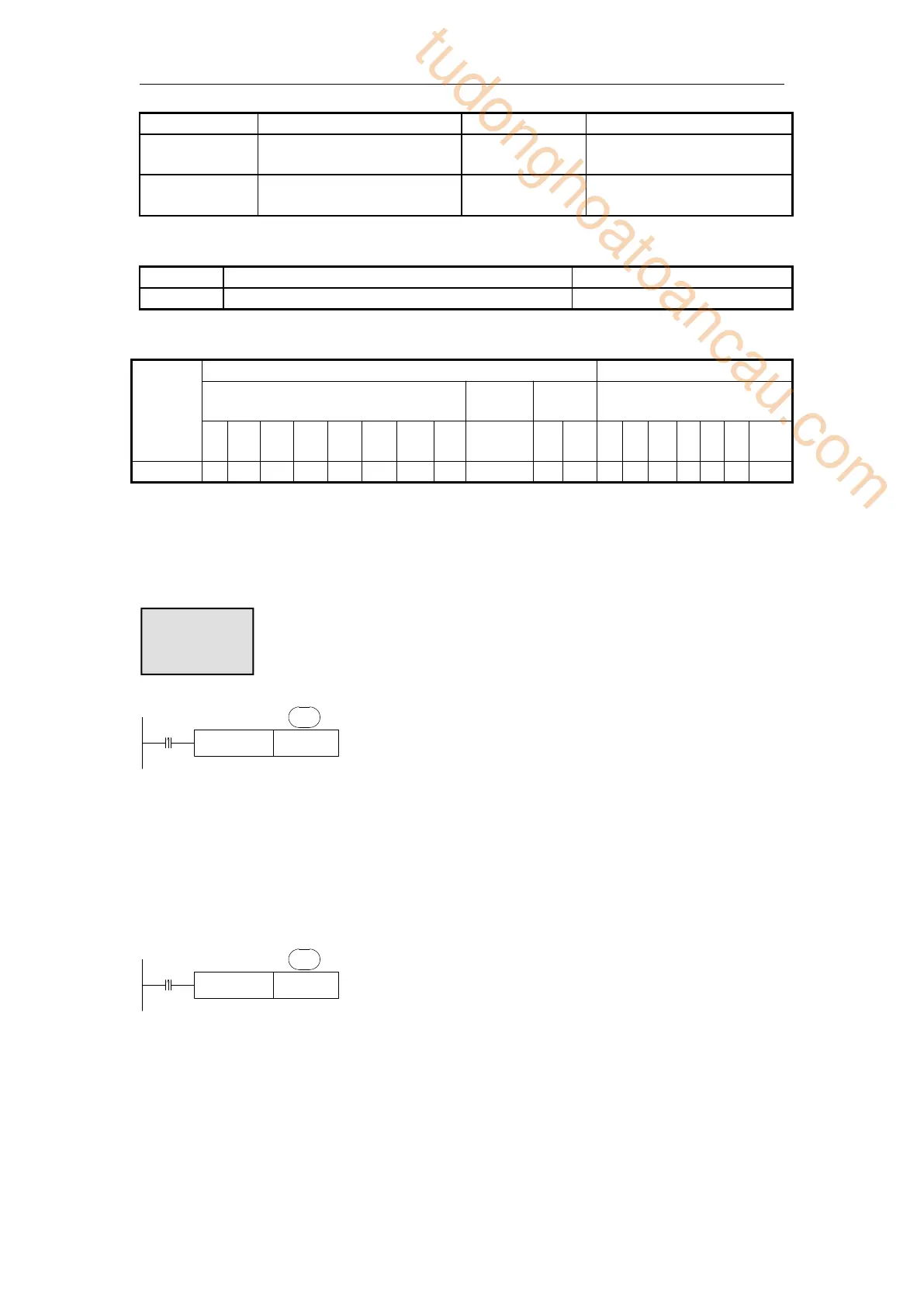

< Increment [INC]>

D will increase one when X0 is ON.

For 16 bits operation, when +32767 increase one, it will become -32768; The flag bit will act.

for 32 bits operation, +2147483647 increases one is -2147483647. The flag bit will act.

for 64 bits operation, +9223372036854775807 increases one is -9223372036854775808. The

flag bit will act.

<Decrement [DEC]>

D will decrease one when X1 is ON.

-32767 or -2147483647 decrease one, the result will be +32767 or +2147483647. The flag bit

will act. For 64 bits operation, -9223372036854775808 decrease one is

+9223372036854775807. The flag bit will act.

The addresses of operands in QINC and QDEC instruction must be even.

tudonghoatoancau.com

Loading...

Loading...