Memory Management Unit

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 3-9

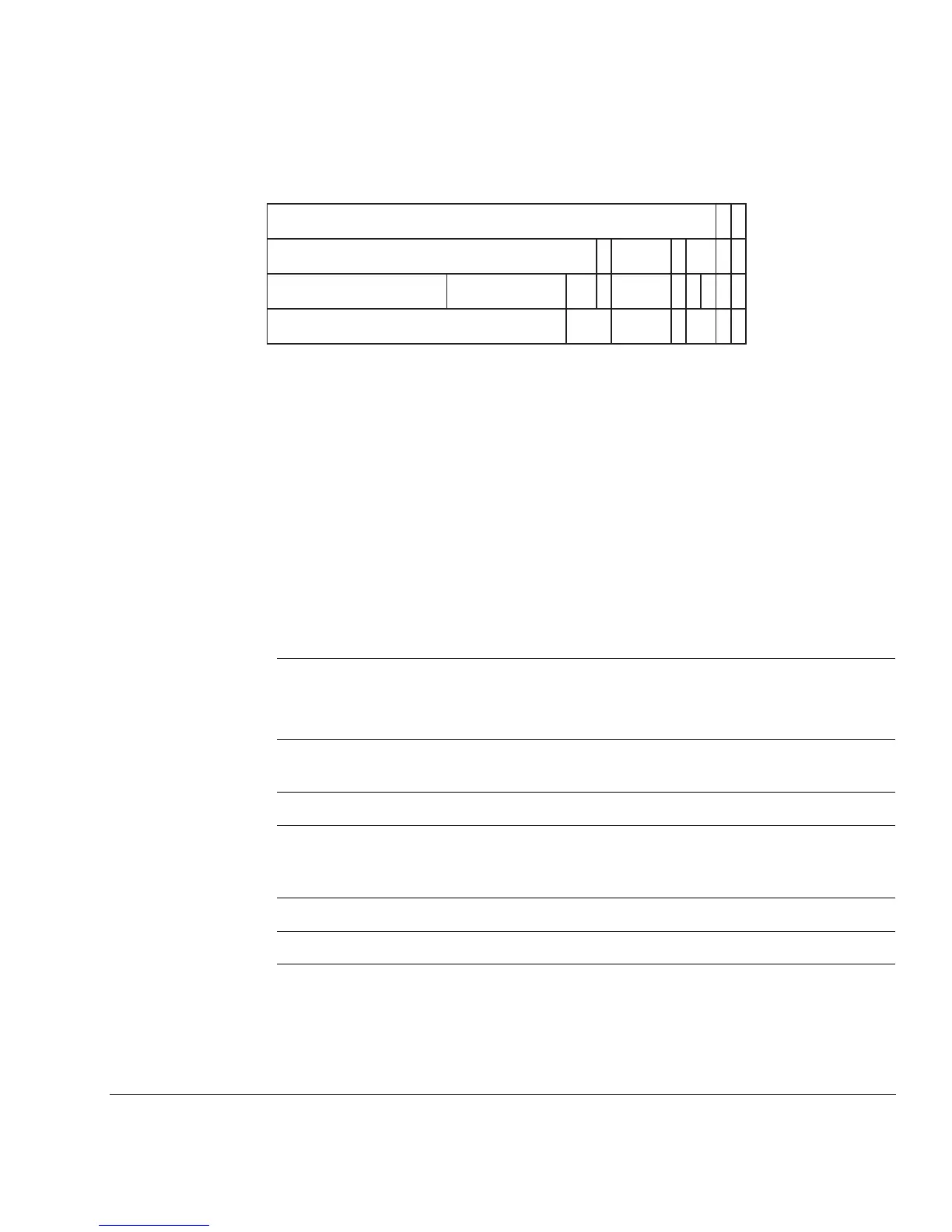

Figure 3-4 First-level descriptor

A section descriptor provides the base address of a 1MB block of memory.

The page table descriptors provide the base address of a page table that contains

second-level descriptors. There are two sizes of page table:

• coarse page tables have 256 entries, splitting the 1MB that the table describes into

4KB blocks

• fine page tables have 1024 entries, splitting the 1MB that the table describes into

1KB blocks.

First-level descriptor bit assignments are shown in Table 3-2.

31 20 19 12 11 10 9 8 5 4 3 2 1 0

0 0

Coarse page table base address Domain 1 0 1

Section base address AP Domain 1 C B 1 0

Fine page table base address Domain 1 1 1

Fault

Coarse page table

Section

Fine page table

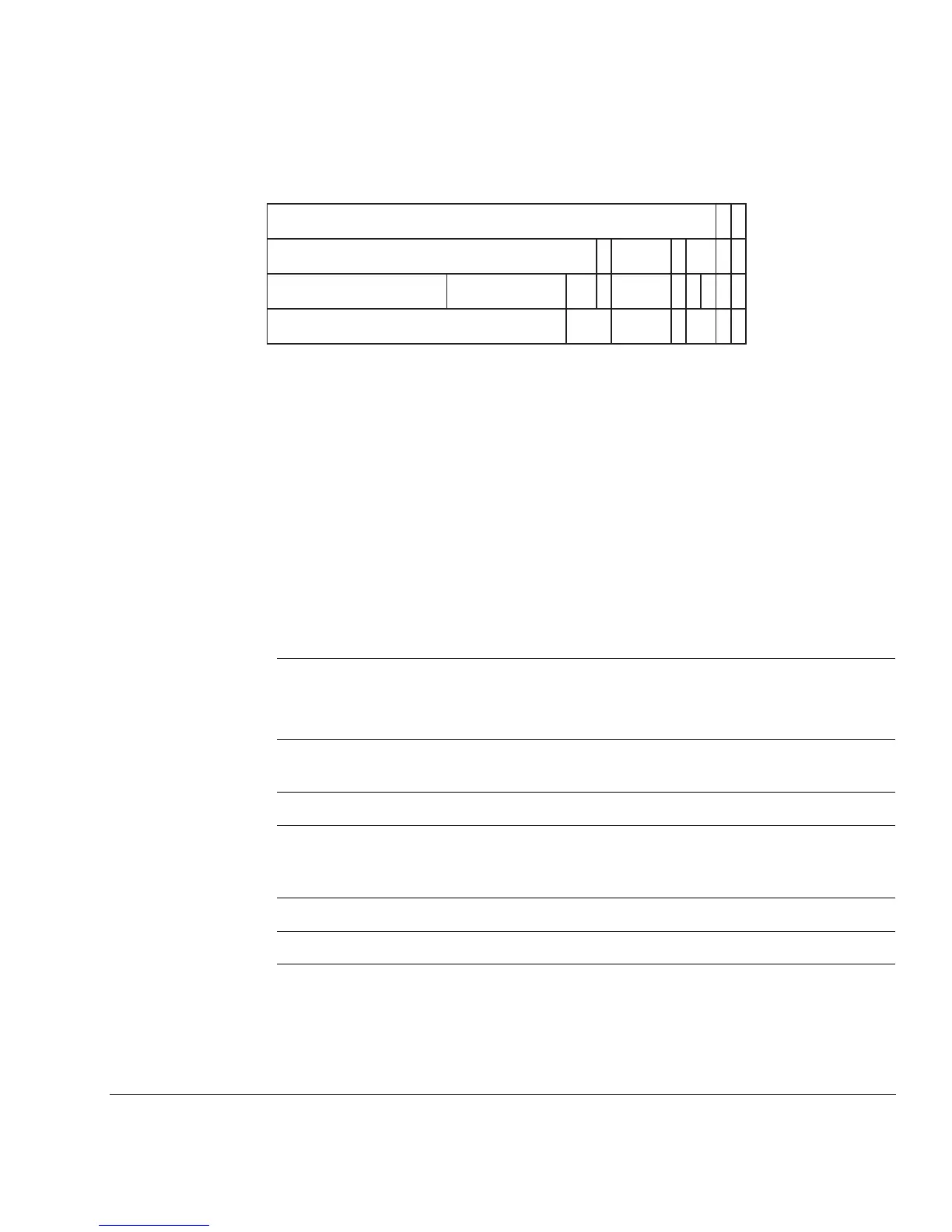

Table 3-2 First-level descriptor bits

Bits

Description

Section Coarse Fine

[31:20] [31:10] [31:12] These bits form the corresponding bits of the physical

address.

[19:12] - - Should Be Zero.

[11:10] - - Access permission bits. Access permissions and domains on

page 3-3 and Fault address and fault status registers on

page 3-21 show how to interpret the access permission bits.

[9] [9] [11:9] Should Be Zero.

[8:5] [8:5] [8:5] Domain control bits.

[4] [4] [4] Must be 1.

Loading...

Loading...