Coprocessor Interface

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 8-7

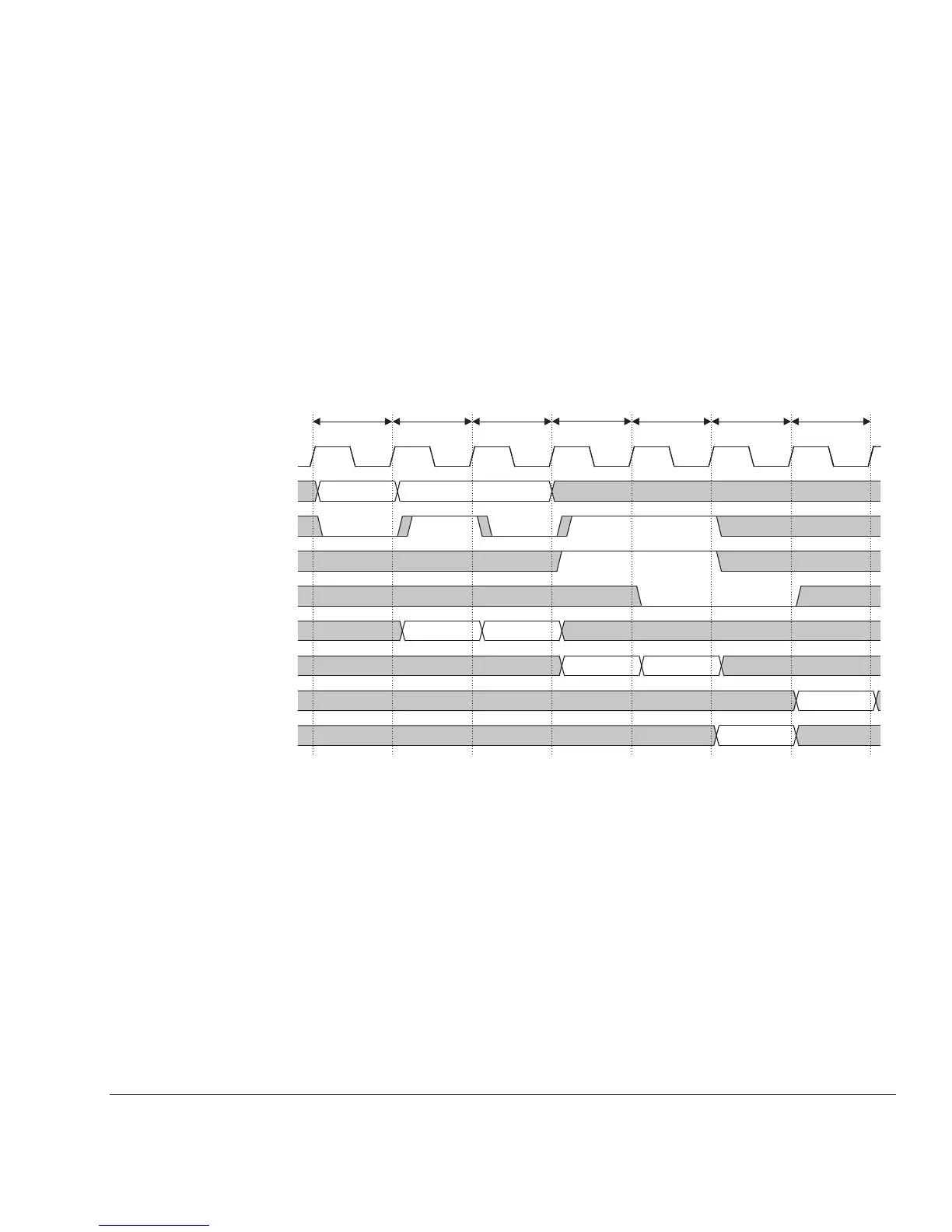

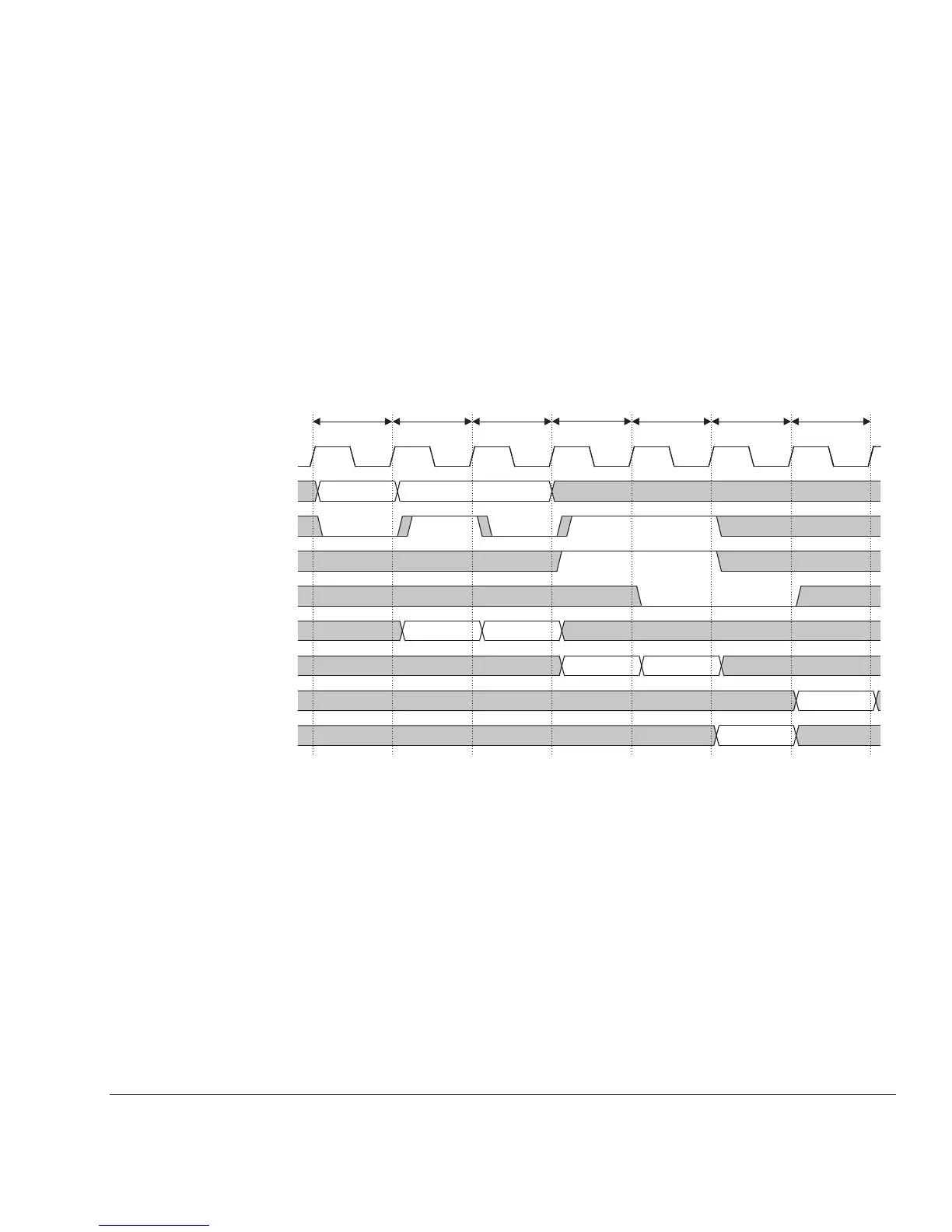

8.3.1 Interlocked MCR

If the data for an MCR operation is not available inside the ARM9EJ-S core pipeline

during its first Decode cycle, then the ARM9EJ-S core pipeline interlocks for one or

more cycles until the data is available. An example of this is where the register being

transferred is the destination from a preceding LDR instruction. In this situation the

MCR instruction enters the Decode stage of the coprocessor pipeline, and remains there

for a number of cycles before entering the Execute stage.

Figure 8-5 shows an example of an interlocked MCR.

Figure 8-5 Interlocked MCR

MCR/MRC

WAIT

LAST Ignored

Coproc data

Decode

(interlock)

Execute

(WAIT)

Execute

(LAST)

Memory Write

CPLATECANCEL

CHSDE[1:0]

CHSEX[1:0]

CPDOUT[31:0]

MCR

CPDIN[31:0]

MRC

CPPASS

CPINSTR[31:0]

nCPMREQ

CLK

Coprocessor pipeline

Decode

WAIT

Fetch

Loading...

Loading...