Tightly-Coupled Memory Interface

5-14 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

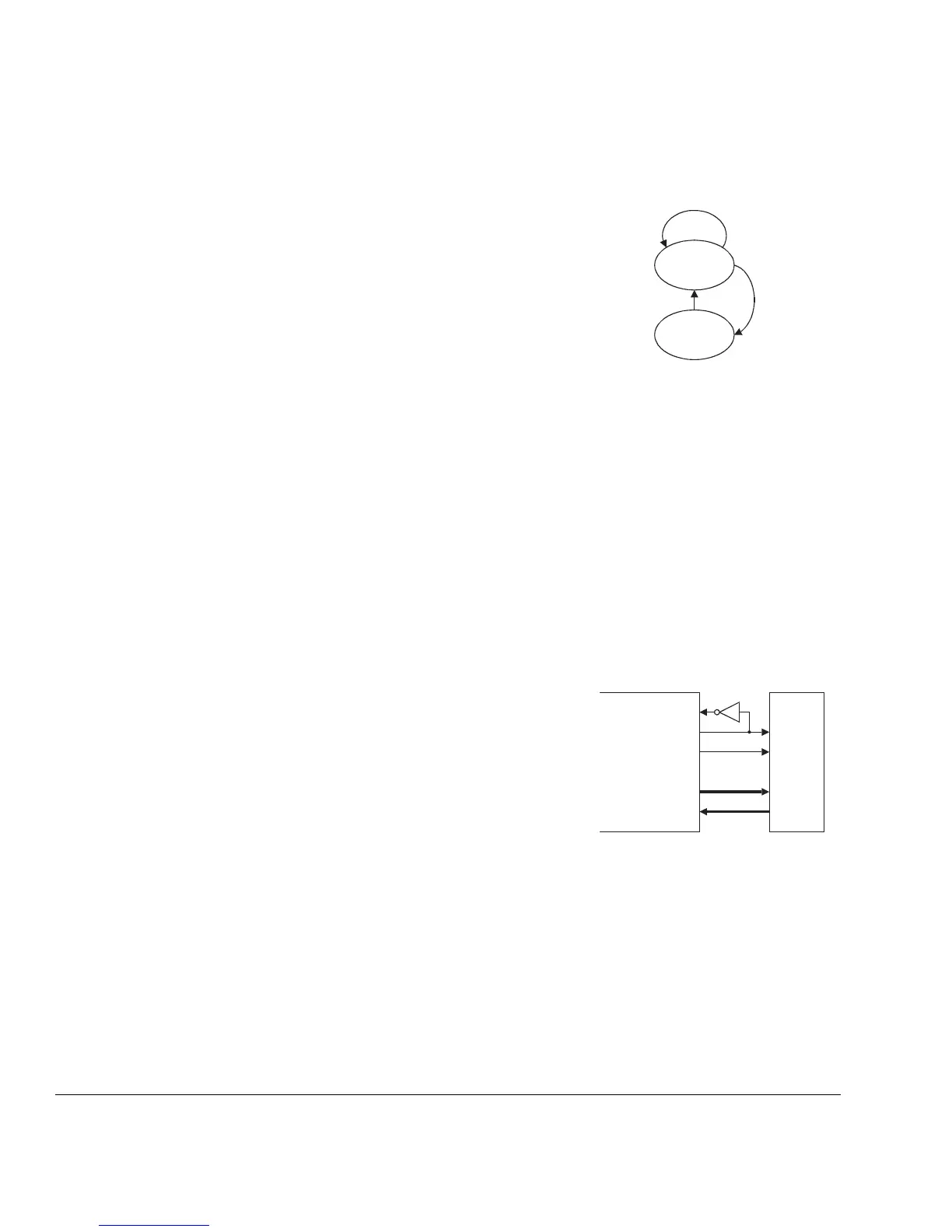

Figure 5-7 State machine for generating a single wait state

In the WAIT state IRWAIT is asserted. In the COMPLETE state IRWAIT is

deasserted.

Certain types of memories can have different access penalties depending on whether an

access is sequential or nonsequential. The IRSEQ/DRSEQ signals indicate if an access

is sequential in the request cycle for an access, and are held HIGH during waited cycles.

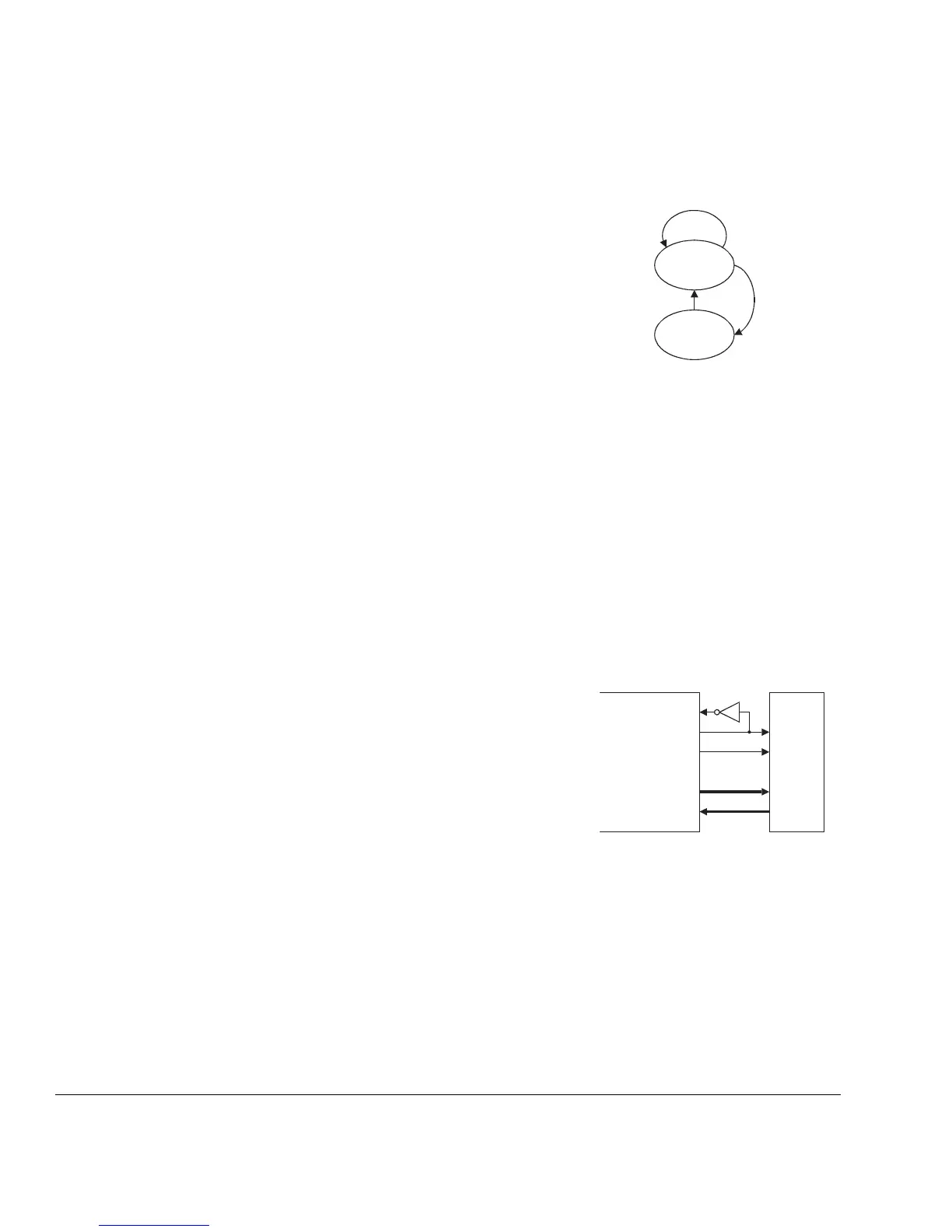

This behaviour enables a loopback arrangement, where the SEQ output can be fed

directly back into the WA I T input through an inverter to produce a single cycle wait

state for nonsequential accesses as shown in Figure 5-8.

Figure 5-8 Loopback of SEQ to produce a single cycle wait state

The cycle timing of the circuit shown in Figure 5-8 is shown in Figure 5-9 on page 5-15.

COMPLETE

WAIT

IRCS = 1

IRCS = 0

TCM

IRRD[31:0]

IRADDR[17:0]

IRCS

IRSEQ

IRWAIT

Loading...

Loading...