Coprocessor Interface

8-8 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

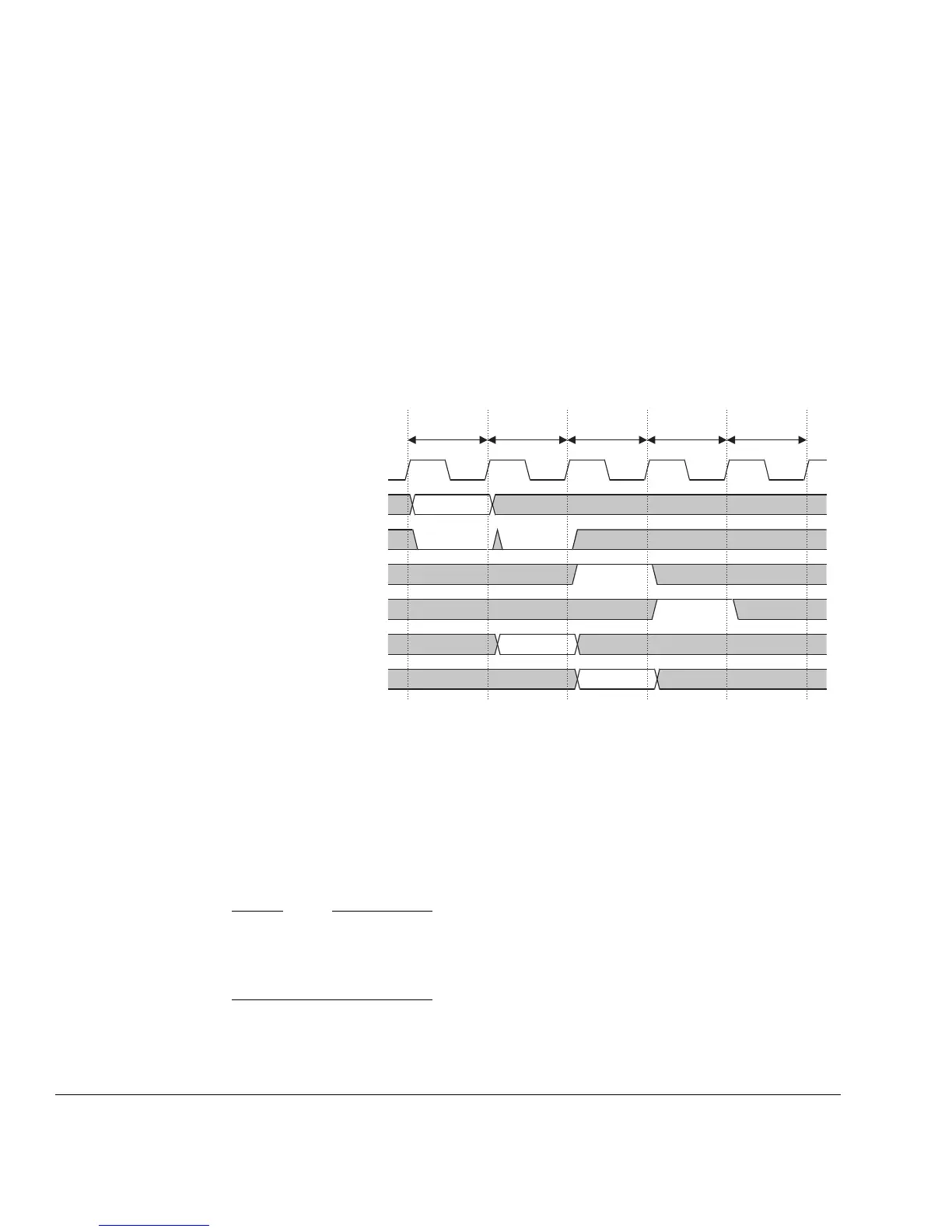

8.4 CDP

CDP

instructions usually execute in a single cycle. Like all the previous cycles,

nCPMREQ is driven LOW to signal when an instruction is entering the Decode and

then the Execute stage of the pipeline. If the instruction is to be executed then the

CPPASS signal is driven HIGH during Execute. If the coprocessor can execute the

instruction immediately it drives CHSDE[1:0] with LAST. If the instruction requires a

busy-wait cycle, then the coprocessor drives CHSDE[1:0] with WAIT and then

CHSEX[1:0] with LAST. Figure 8-6 shows a CDP that is canceled due to the previous

instruction causing a Data Abort.

Figure 8-6 Latecanceled CDP

The CDP instruction enters the Execute stage of the pipeline and is signaled to execute

by CPPASS. In the following phase CPLATECANCEL is asserted. This causes the

coprocessor to terminate execution of the CDP instruction and for it to cause no state

changes to the coprocessor.

Note

CPLATECANCEL can be asserted during the Memory cycle or during the Execute

cycle. The coprocessor must be able to handle instruction aborts during these two

stages.

Execute Memory

CLK

CPINSTR[31:0]

nCPMREQ

CPPASS

CPLATECANCEL

CHSDE[1:0]

CHSEX[1:0]

Coprocessor pipeline

Instruction

aborted

Fetch

CPRT

LAST

Ignored

Decode

Loading...

Loading...