Tightly-Coupled Memory Interface

5-28 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

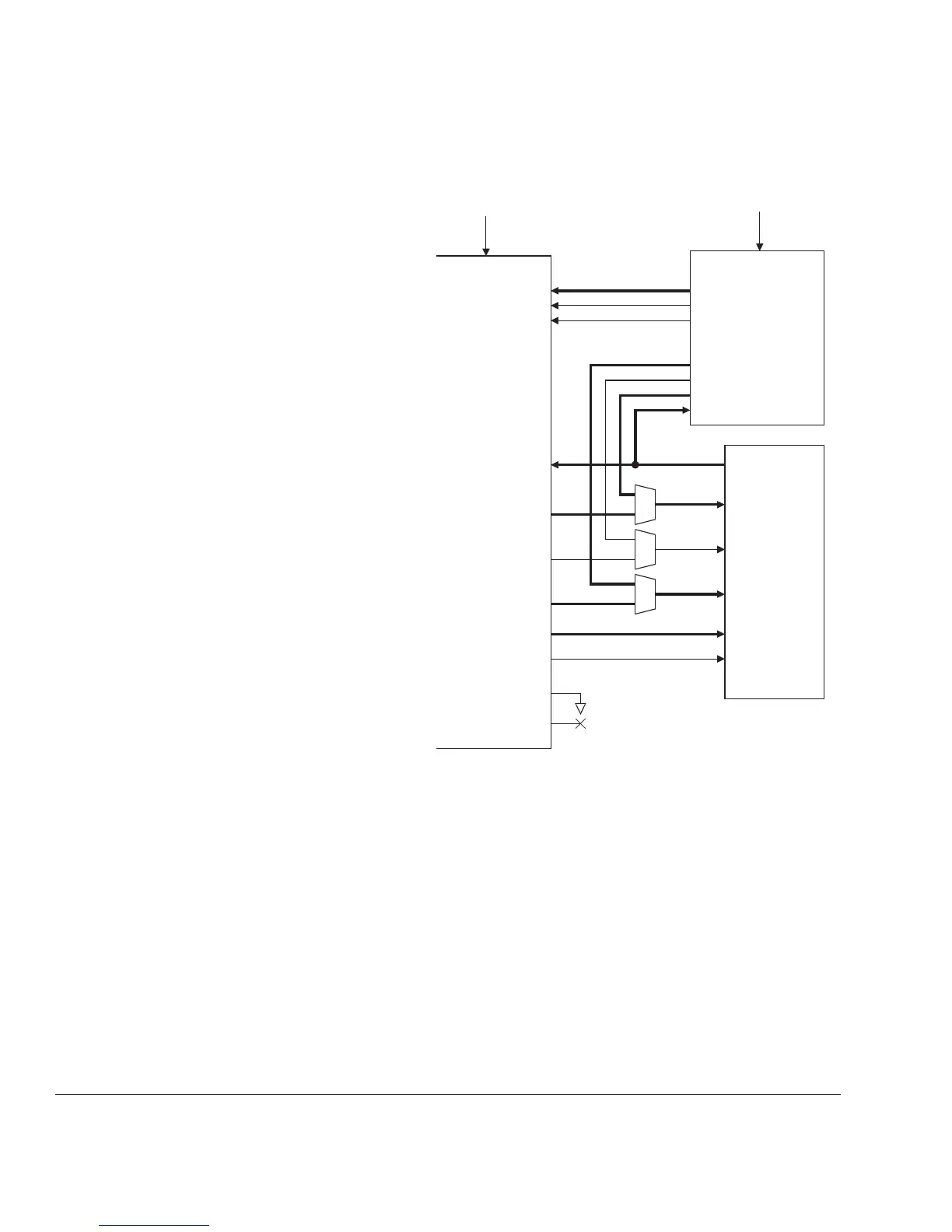

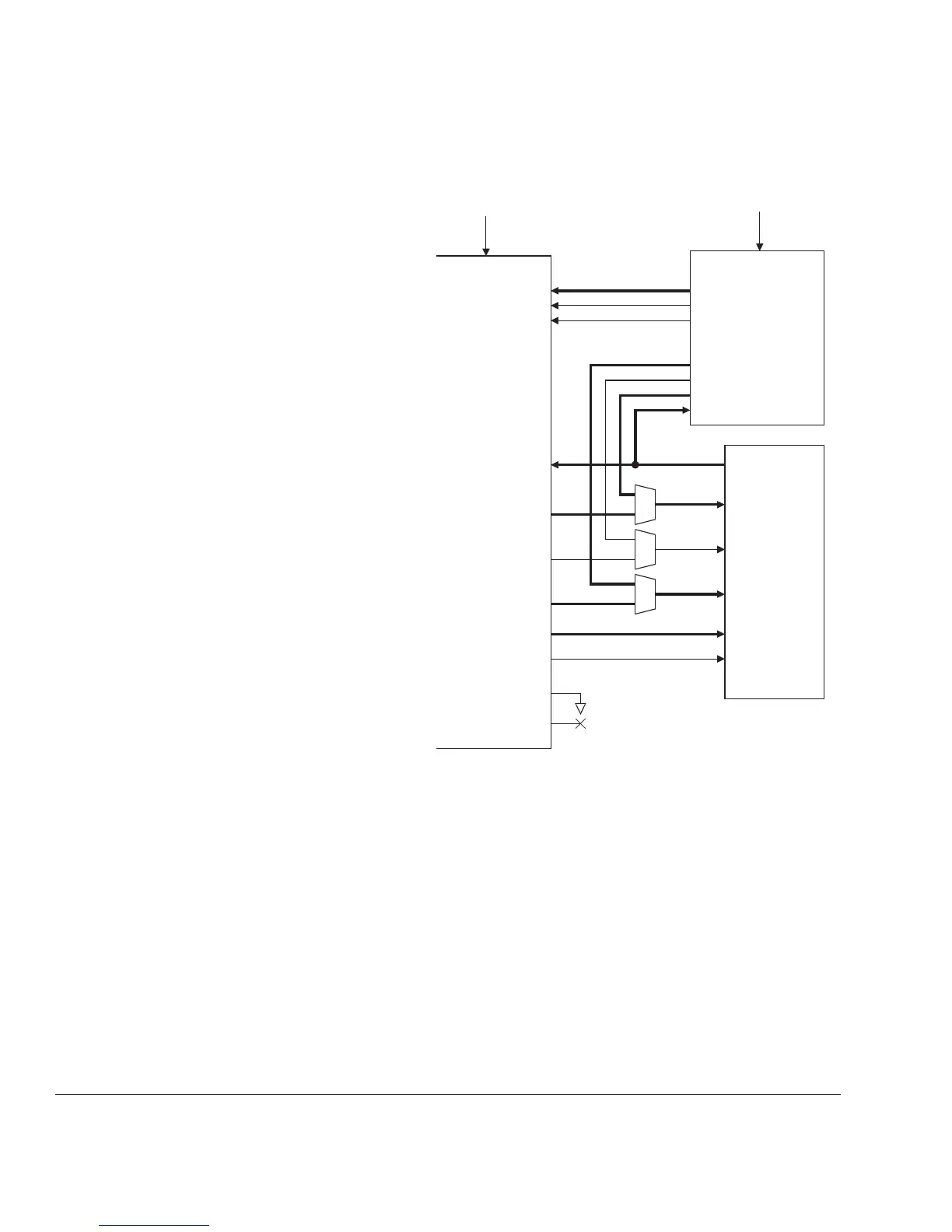

Figure 5-19 TCM test access using BIST

This is similar to the previous DMA example. However, for BIST testing it is necessary

for the BIST controller to be able to force the memory chip select to both HIGH and

LOW values. This requirement means that it is necessary to hold the ARM926EJ-S core

in such a state that the internal value of the chip select is guranteed to be LOW. This can

be done by holding the ARM926EJ-S in reset (HRESETn LOW) during TCM memory

BIST testing. Note that this requires that HRESETn cannot also be used as a reset

control to the BIST controller.

SRAM

DRWD[31:0]

BISTRD[31:0]

DRWBL[3:0]

DRDMAADDR[17:0]

CS

WD[31:0]

ARM926EJ-S

1

0

BIST

1

0

1

0

BISTWBL[3:0]

BISTnRW

BISTWD[31:0]

BISTEN

BISTADDR[17:0]

DRDMAEN

DRDMACS

DRnRW

RD[31:0]

WBL[3:0]

nRW

A[17:0]DRADDR[17:0]

DRCS

DRWAIT

DRSEQ

BISTCS

BISTRSTn

HRESETn

Loading...

Loading...