Coprocessor Interface

8-12 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

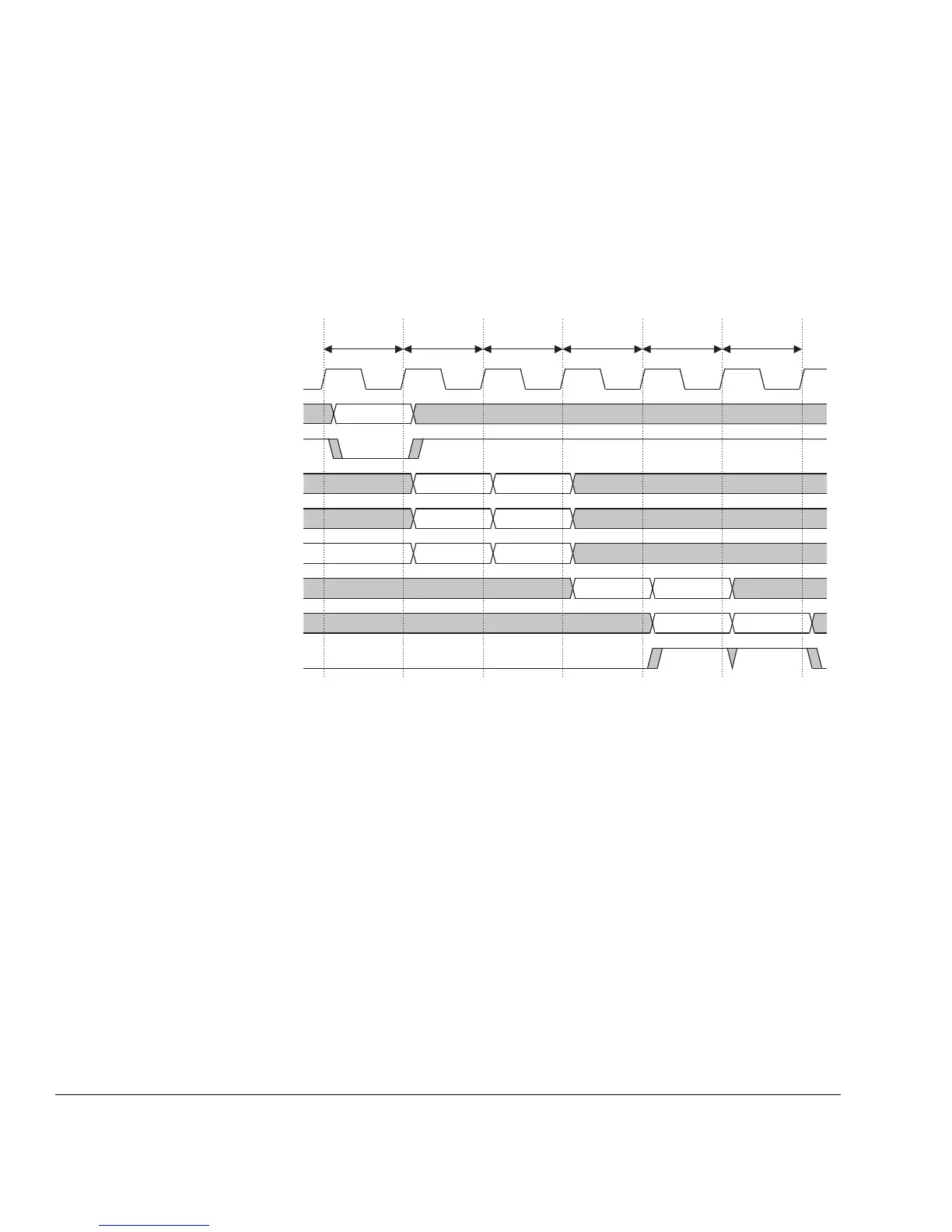

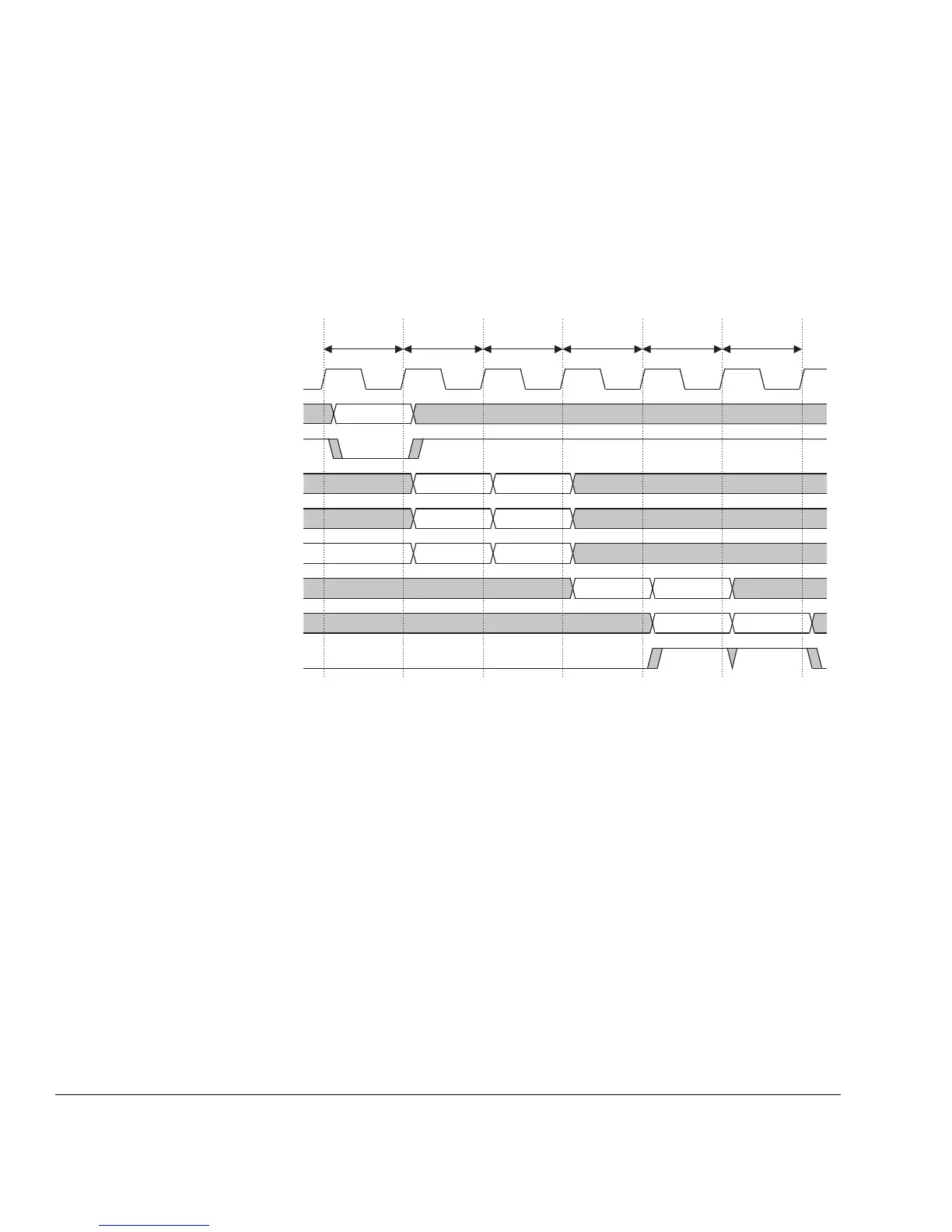

8.8 CPABORT

The CPABORT signal being asserted HIGH indicates that an

LDC

/

STC

instruction has

aborted. CPABORT is asserted in the cycle after the Memory stage of the aborting

LDC/STC instruction. This is shown in Figure 8-9.

Figure 8-9 CPBURST and CPABORT timing

CLK

CPINSTR[31:0]

nCPMREQ

CHSDE[1:0]

CHSEX[1:0]

Coprocessor pipeline

Execute 1

Fetch

LDC/STC

GO

Decode

Memory 1 Write 1

ABSENT LAST

Execute 2 Memory 2 Write 2

ABSENT

0001 00000000

CPBURST

CPDIN[3:0]

CPDOUT[3:0]

CPABORT

Loading...

Loading...