Tightly-Coupled Memory Interface

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 5-11

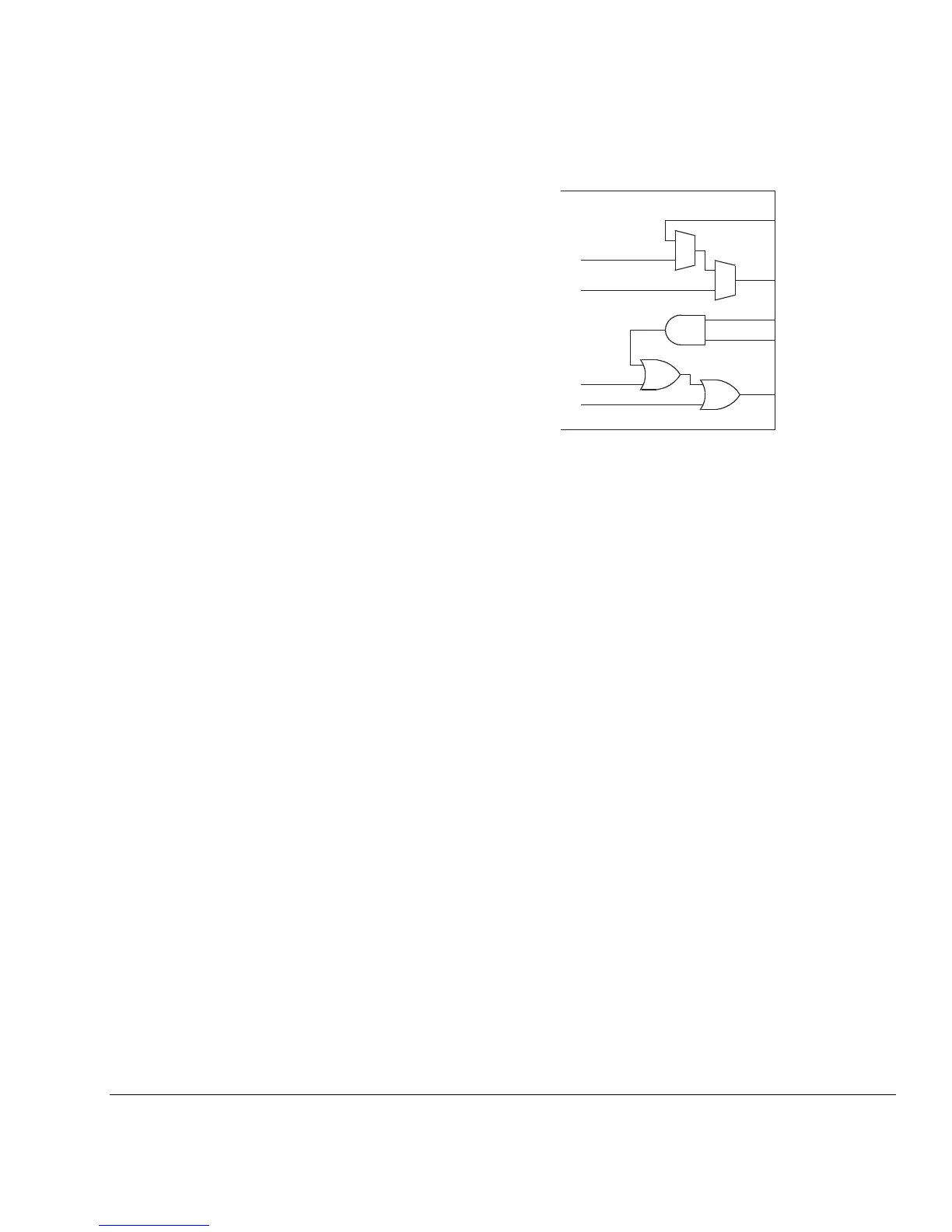

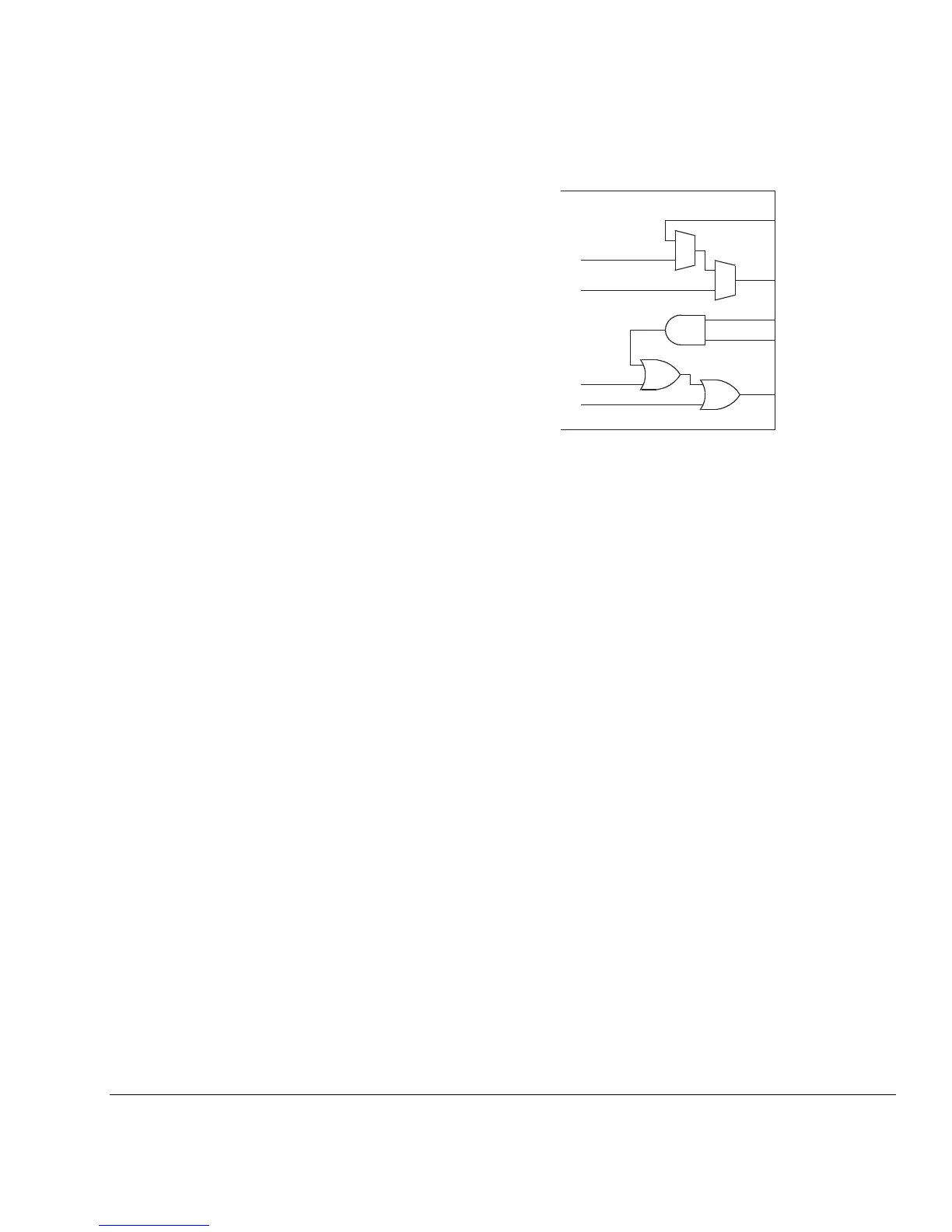

Figure 5-4 Relationship between DRDMAEN, DRDMACS, DRDMAADDR, DRADDR and DRCS

Internal to the ARM926EJ-S processor there are multiple sources for both the address

and chip-select outputs. The address and chip-select outputs of the TCM interface are

timing critical, however not all of the internal sources are timing critical. By combining

the DMA inputs with non-critical address and chip-select signals, DMA can be done

without impacting timing on these outputs. All other TCM interface outputs are non

timing critical, and can be multiplexed externally.

The logic used to combine the DMA chip-select with the internal chip-select signals is

designed so that if the DMA inputs are selected then the DMA chip-select is also

asserted. If this is not the case then the chip-select output value is non-deterministic

unless it is known that the TCM interface is an idle state, as indicated by the DRIDLE

or STANDBYWFI signals.

Figure 5-5 on page 5-12 shows an example of how DMA accesses interact with normal

DTCM accesses.

1

0

Late address

Early address

1

0

Early CS

Late CS

DRDMAADDR

DRADDR

DRDMAEN

DRDMACS

DRCS

Loading...

Loading...