Tightly-Coupled Memory Interface

5-24 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

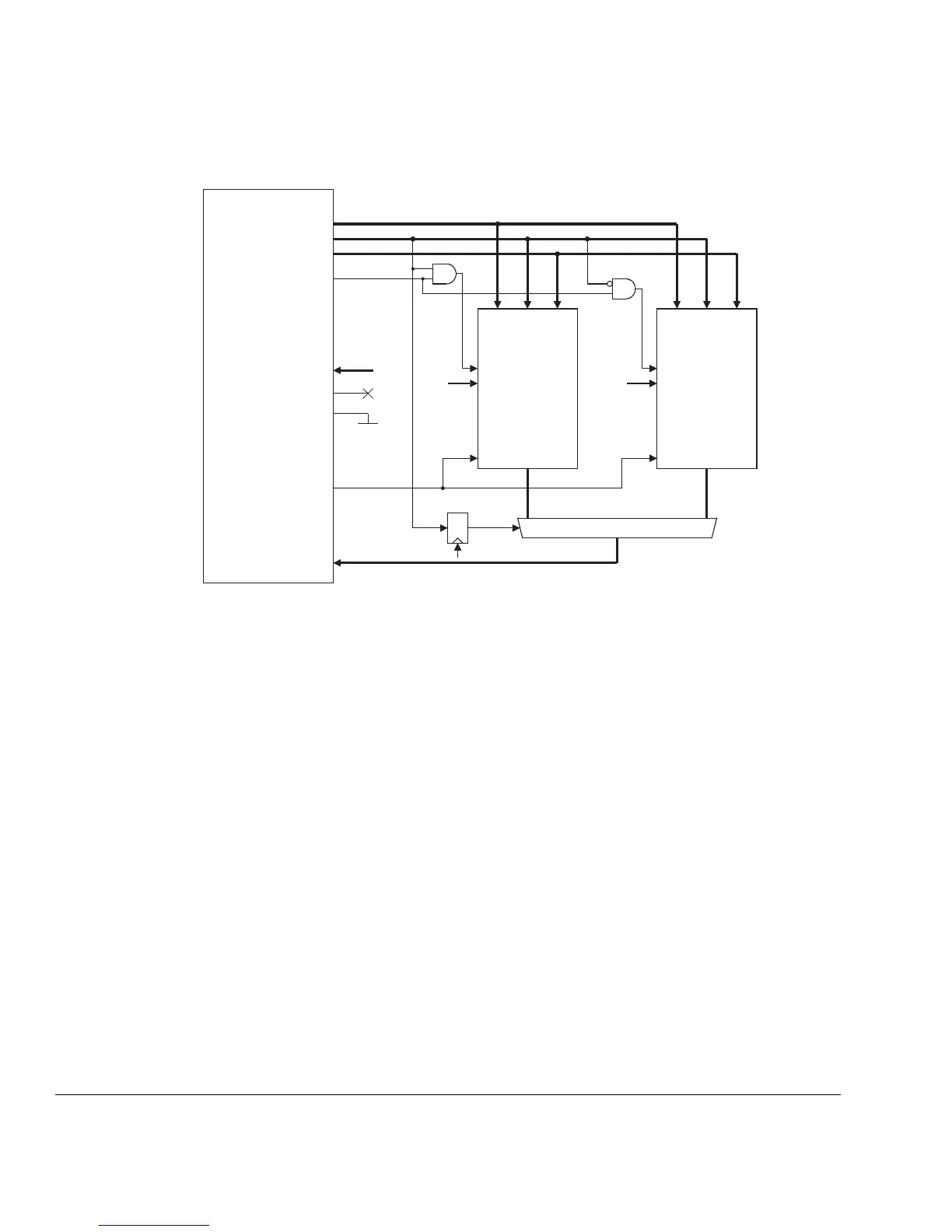

Figure 5-15 Optimizing for speed

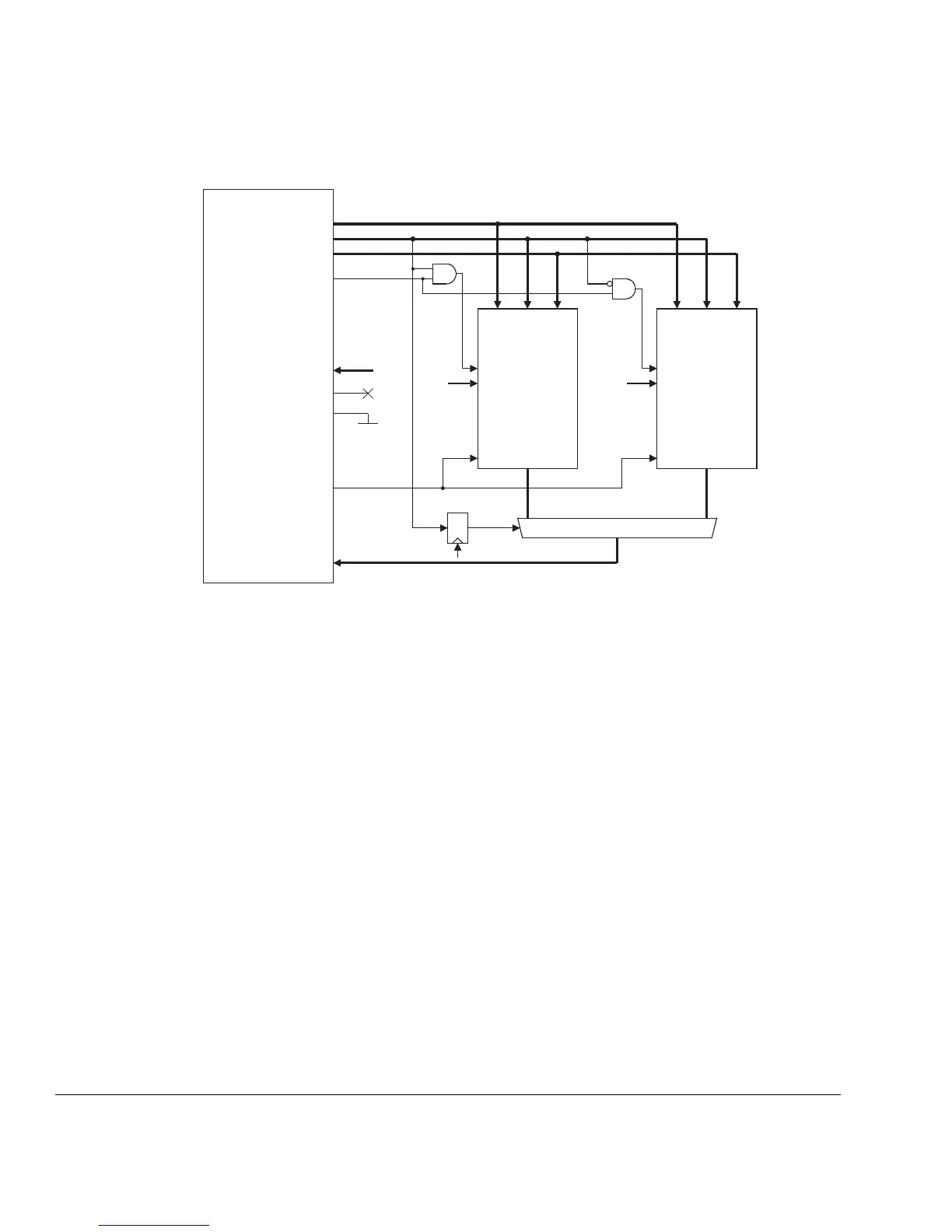

5.5.4 Sequential ROM example

The diagram in Figure 5-16 on page 5-25 shows an example of a TCM sub-system that

uses wait states for nonsequential accesses. The ROM used to hold instructions can

cycle at the same frequency as the ARM926EJ-S processor it is interfaced to. However,

the memory access time for the ROM (time from chip-select/address to data out) is not

fast enough to be directly interfaced to the ARM926EJ-S processor.

DRCS

DRSEQ

DRWAIT

ARM926EJ-S

RAM 64KB

CLK

CS DOUT[31:0]

RAM 64KB

CLK

CS DOUT[31:0]

DRRD[31:0]

DRADDR[13:0]

DRWD[31:0]

DRADDR[17:0]

DRWBL[3:0]

DRWD[31:0]

CLK

DIN[31:0] BW[3:0]

A[13:0]

DIN[31:0] BW[3:0]

A[13:0]

DRADDR[14]

DRADDR[14]

WE

WE

DRnRW

DRSIZE[3:0] b1000

Bank 1

Bank 0

DRWBL[3:0]

Loading...

Loading...