Caches and Write Buffer

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 4-11

• the ARM926EJ-S caches are four-way Associative

• the range of tags addressed by the Index define a Way

• the number of tags in a Way is the number of Sets, NSETS.

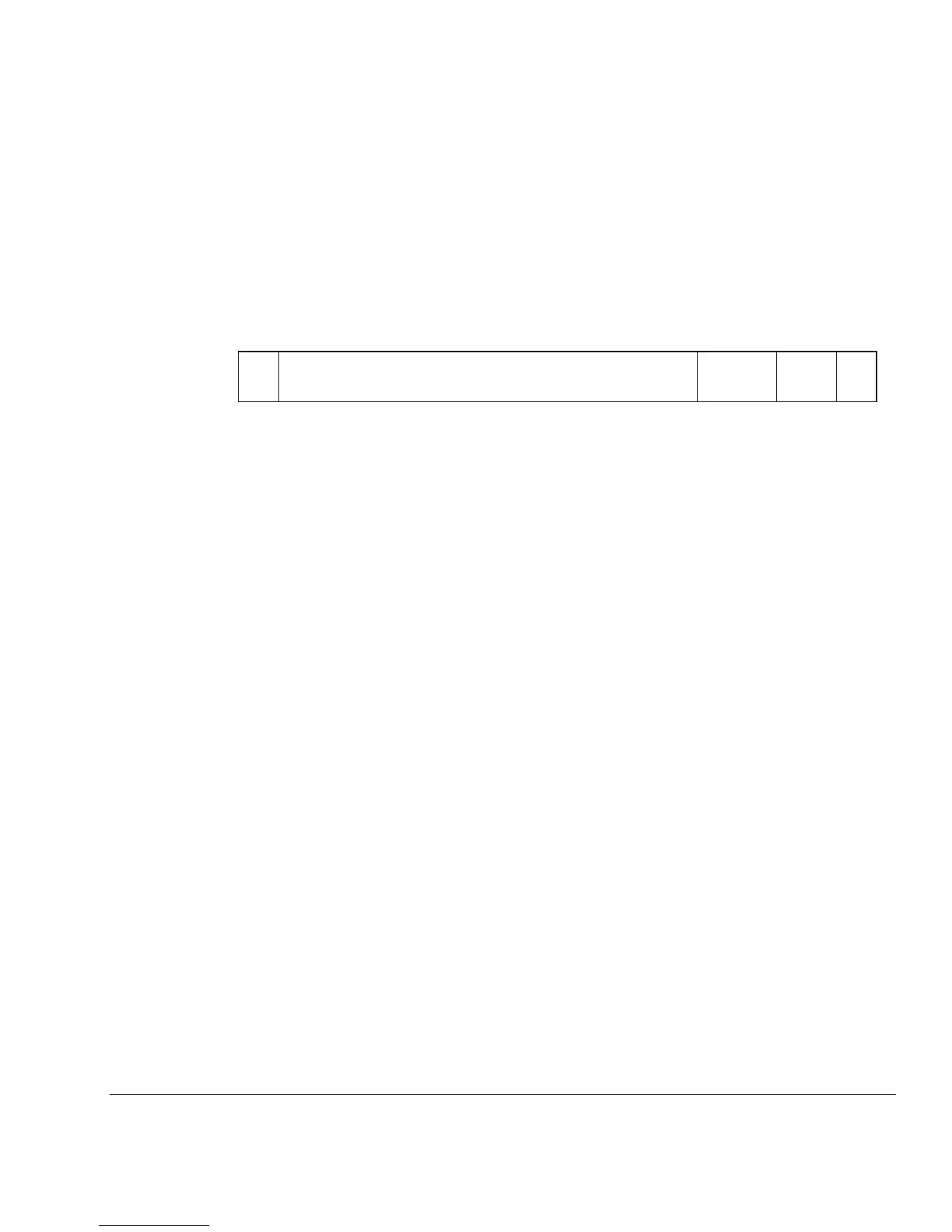

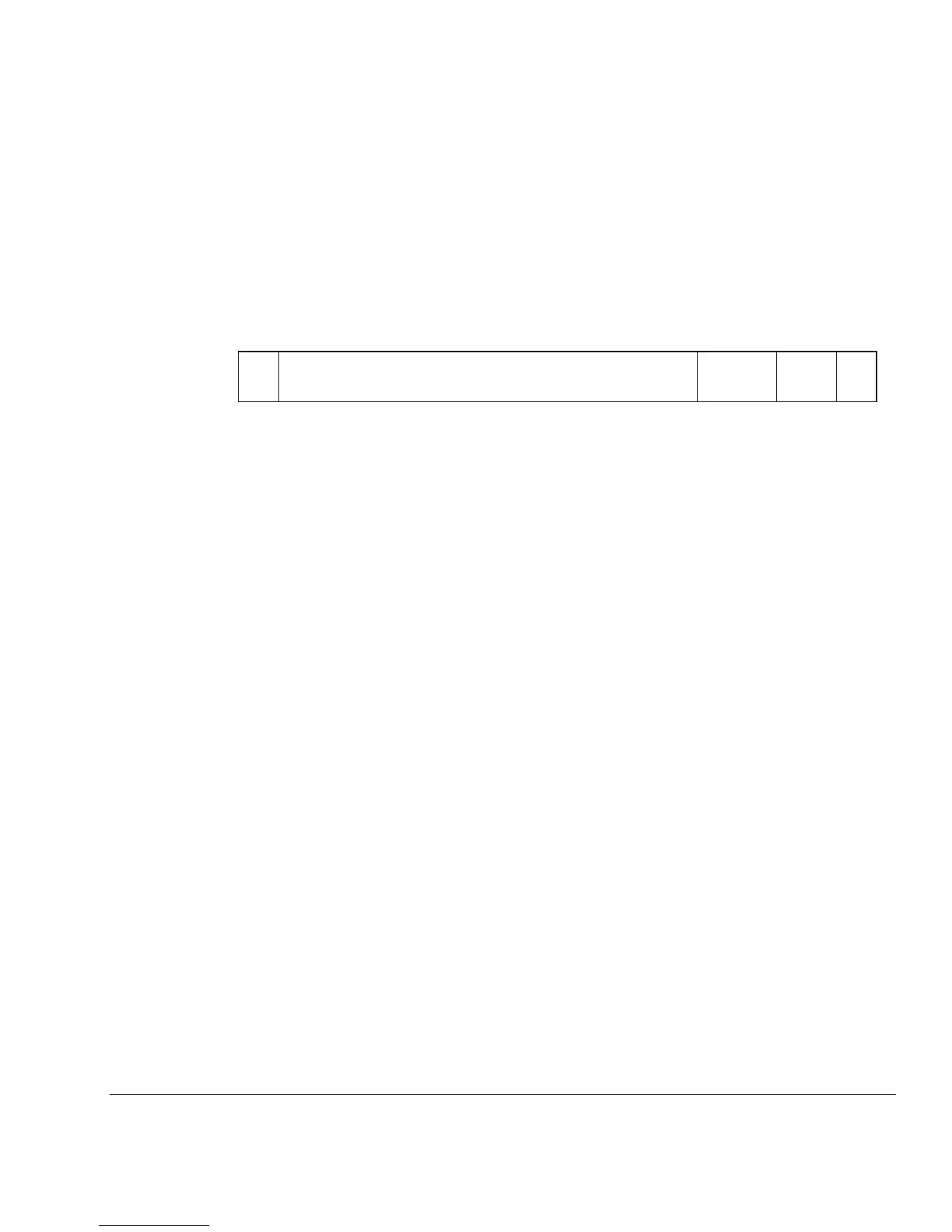

The Set/Way/Word format for ARM926EJ-S caches is shown in Figure 4-3.

Figure 4-3 ARM926EJ-S cache Set/Way/Word format

In Figure 4-3:

A = log

2

Associativity.

For example, for a four-way cache A = 2.

S = log

2

NSETS.

Way SBZ

Set select

(= Index)

Word SBZ

31

32-A

31-A S+5 S+4 5 4 2 1 0

Loading...

Loading...