Coprocessor Interface

8-6 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

8.3 MCR/MRC

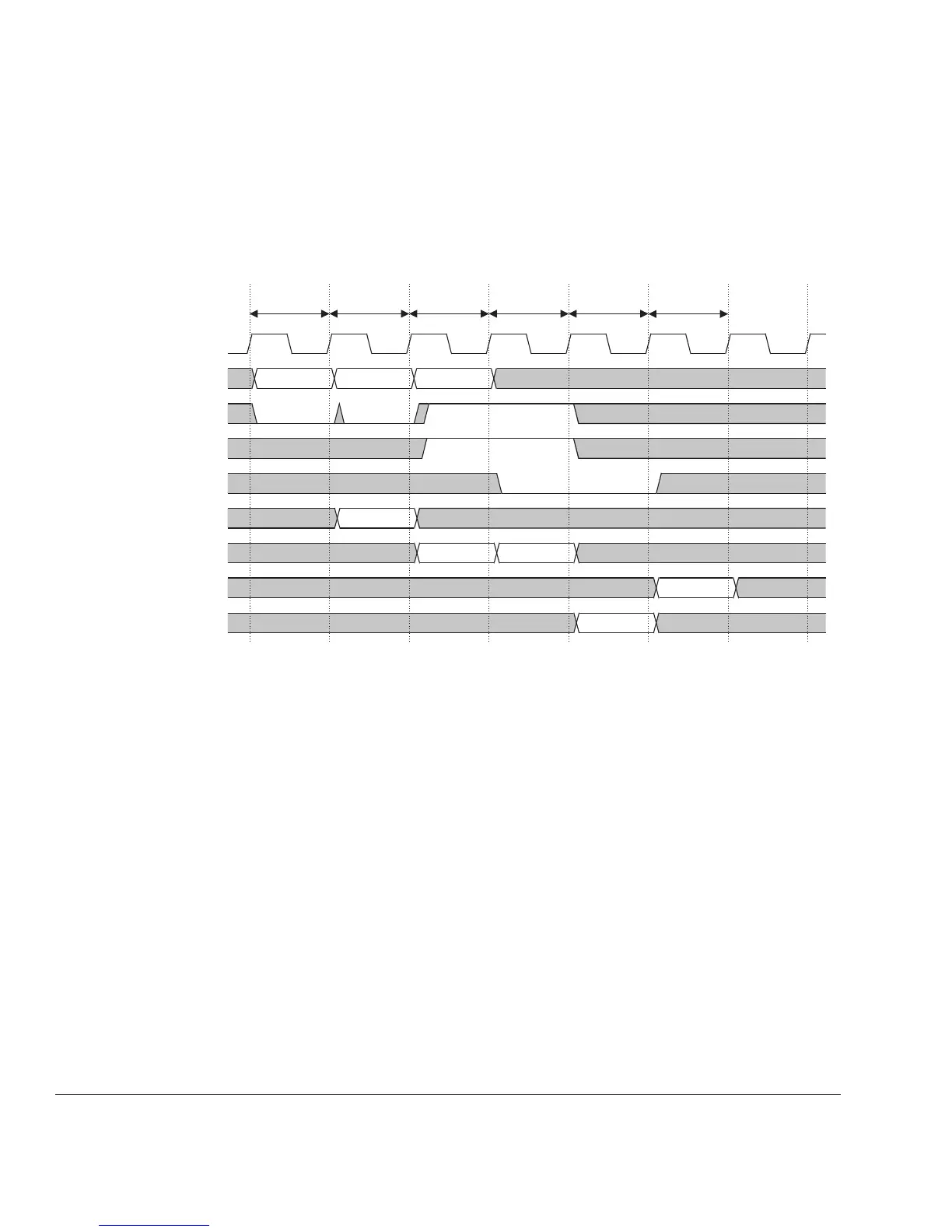

These cycles look very similar to STC/LDC. An example with a busy-wait state is

shown in Figure 8-4.

Figure 8-4 MCR/MRC cycle timing

First, nCPMREQ is driven LOW to indicate that the instruction on CPINSTR is

entering the Decode stage of the pipeline. This coprocessor decodes the new instruction

and drives CHSDE[1:0] as required.

In the next cycle, nCPMREQ is driven LOW to indicate that the instruction has now

been issued to the Execute stage. If the condition codes pass and the instruction is to be

executed, the CPPASS signal is driven HIGH and the CHSDE[1:0] handshake bus is

examined (it is ignored in all other cases).

For any successive execute cycles the CHSEX[1:0] handshake bus is examined. When

the LAST condition is observed, the instruction is committed. In the case of an MCR,

the CPDOUT[31:0] bus is driven with the register data during the coprocessor Write

stage. In the case of an MRC, CPDIN[31:0] is sampled at the end of the ARM9EJ-S

memory stage and written to the destination register during the next cycle.

Decode

Execute

(WAIT)

Execute

(LAST)

Memory

CLK

CPINSTR[31:0]

nCPMREQ

CPPASS

CPLATECANCEL

CHSDE[1:0]

CHSEX[1:0]

Coprocessor pipeline

Write

Fetch

CPDOUT[31:0]

MCR

CPDIN[31:0]

MRC

MCR/MRC

WAIT

LAST Ignored

Coproc data

Coproc data

Loading...

Loading...