Tightly-Coupled Memory Interface

5-12 Copyright © 2001-2003 ARM Limited. All rights reserved. ARM DDI0198D

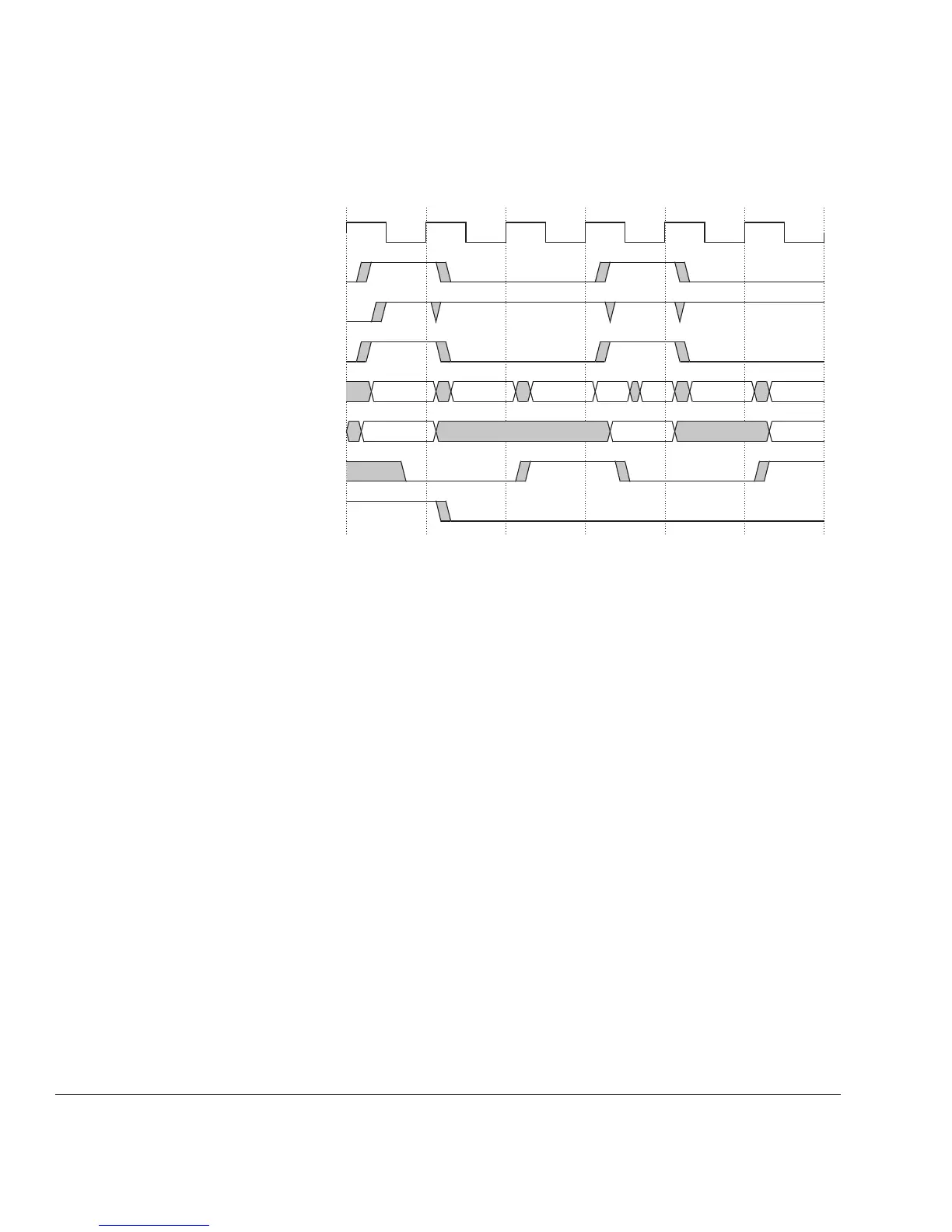

Figure 5-5 DMA access interaction with normal DTCM accesses

In cycle T1, the ARM926EJ-S internal TCM controller is idle and DRIDLE is asserted.

DRDMAEN is asserted, and consequently the value of DRDMAADDR is propagated

onto DRADDR, and DRCS is asserted (DRDMACS = 1). DRSEQ is forced LOW.

In cycle T2, the ARM926EJ-S internal TCM controller is no longer idle, and DRIDLE

is deasserted. A nonsequential request is made to address B.

In cycle T3, a sequential request is made to address B+1 and DRSEQ is asserted

In cycle T4, the ARM926EJS internal TCM controller attempts to output values

corresponding to a sequential request to address B+2. DRDMAEN is asserted, and the

value of DRADDR and DRSEQ change accordingly. The ARM926EJ-S TCM

controller is stalled.

In cycle T5, DRDMAEN is deasserted and the ARM926EJ-S TCM controller re-issues

the request to address B+2. Because of the intervening DMA access, DRSEQ is

deasserted for the repeated request.

In cycle T6, a sequential request is made to address B+3 and DRSEQ is re-asserted.

DMA accesses can be made to the ITCM using the IRDMAEN, IRDMACS, and

IRDMAADDR signals but, unlike the DTCM, simultaneous access by the

ARM926EJ-S and DMA is not supported. This means that ITCM DMA must not take

place while executing code from the ITCM.

CLK

DRDMAEN

DRCS

DRADDR

A B C B+2

T1 T2 T3 T4 T5 T6

DRDMACS

DRSEQ

DRIDLE

DRDMAADDR

B+1 B+2 B+3

A C B+3

Loading...

Loading...