Programmer’s Model

ARM DDI0198D Copyright © 2001-2003 ARM Limited. All rights reserved. 2-13

MCR p15, 0, <Rd>, c1, c0, 0 ; write control register

All defined control bits are set to zero on reset except the V bit and the B bit. The V bit

is set to zero at reset if the VINITHI signal is LOW, or one if the VINITHI signal is

HIGH. The B bit is set to zero at reset if the BIGENDINIT signal is LOW, or one if the

BIGENDINIT signal is HIGH.

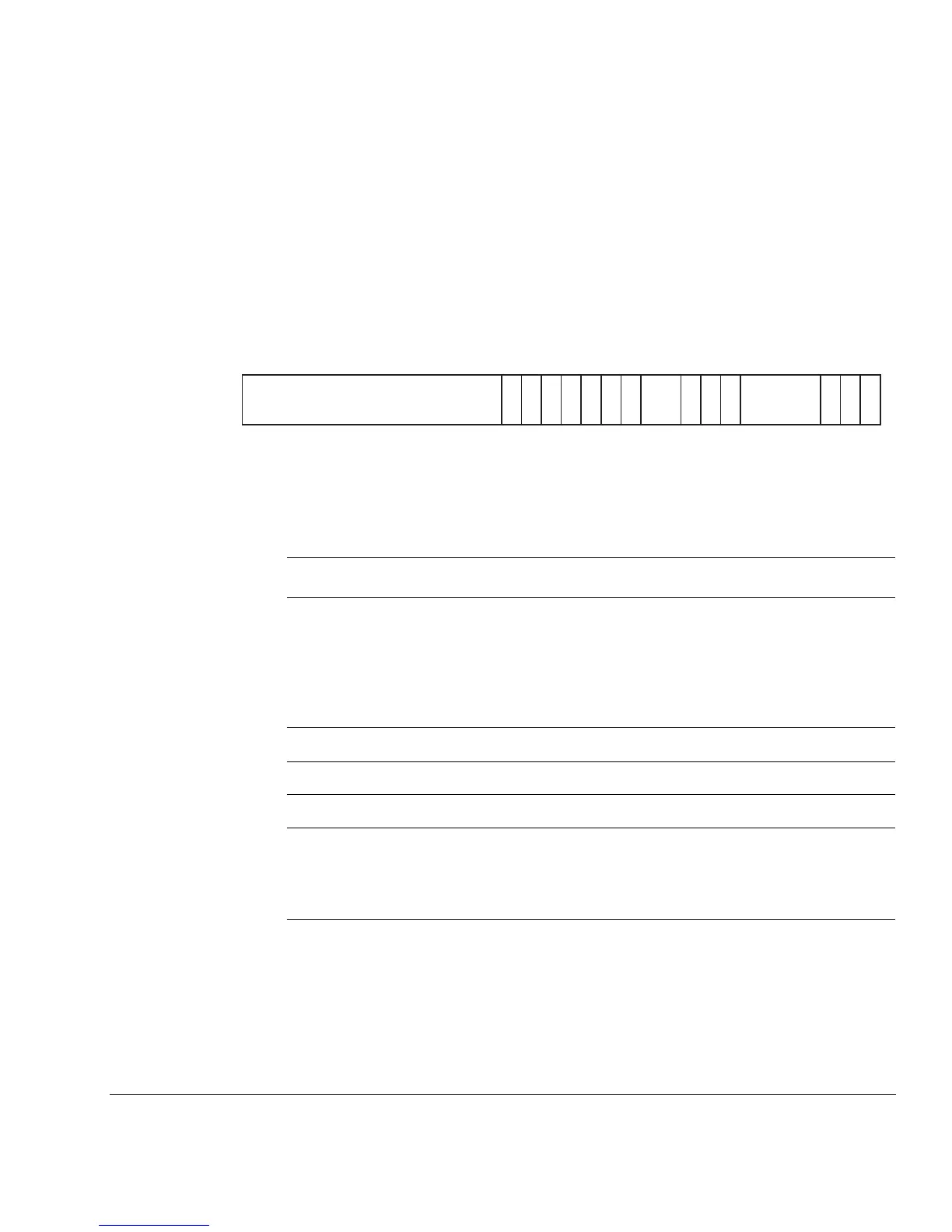

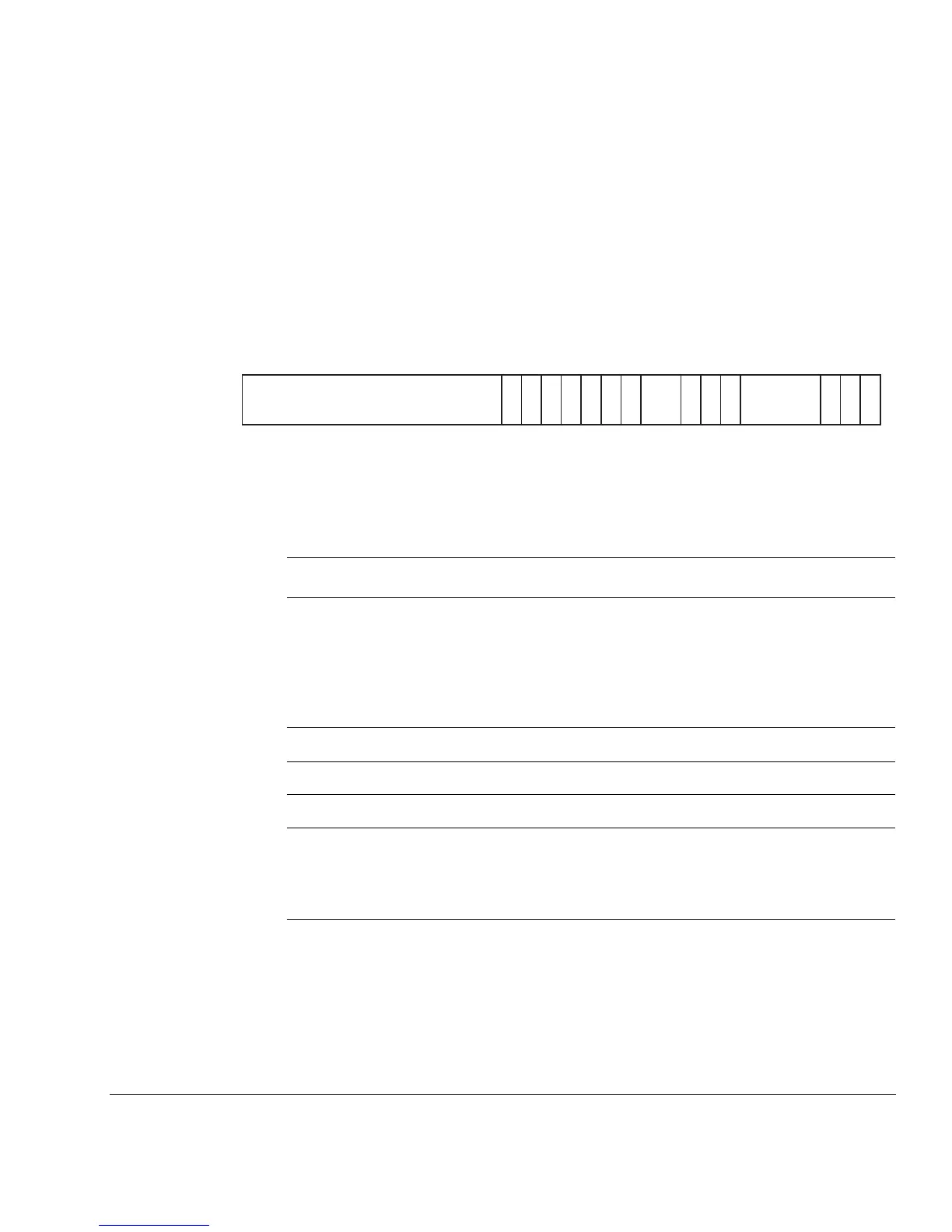

Figure 2-5 shows the format of the Control Register.

Figure 2-5 Control Register format

Table 2-11 describes the functions of the Control Register bits.

MSBZ

31 19 18 17 16 15 14 13 12 11 10 9 8 7 6 3 2 1 0

S

B

O

S

B

Z

S

B

O

L

4

R

R

V I SBZ R S B SBO C A

Table 2-11 Control bit functions register c1

Bit Name Function

[31:19] - Reserved.

When read returns an Unpredictable value.

When written Should Be Zero, or a value read from bits [31:19] on the

same processor.

Using a read-modify-write sequence when modifying this register

provides the greatest future compatibility.

[18] - Reserved, SBO. Read = 1, write = 1.

[17] - Reserved, SBZ. Read = 0, write = 0.

[16] - Reserved, SBO. Read = 1, write = 1.

[15] L4 bit Determines if the T bit is set when load instructions change the PC:

0 = loads to PC set the T bit

1 = loads to PC do not set T bit (ARMv4 behavior).

For more details see the ARM Architecture Reference Manual.

[14] RR bit Replacement strategy for ICache and DCache:

0 = Random replacement

1 = Round-robin replacement.

Loading...

Loading...