Section 3 Exception Handling

Rev. 7.00 Mar 10, 2005 page 86 of 652

REJ09B0042-0700

Bits 1 and 0—IRQ

1

and IRQ

0

Interrupt Request Flags (IRRI1 and IRRI0)

Bit n

IRRIn Description

0

Clearing conditions: (initial value)

When IRRIn = 1, it is cleared by writing 0

1

Setting conditions:

When pin

IRQn

is designated for interrupt input and the designated signal edge is

input

(n = 1 or 0)

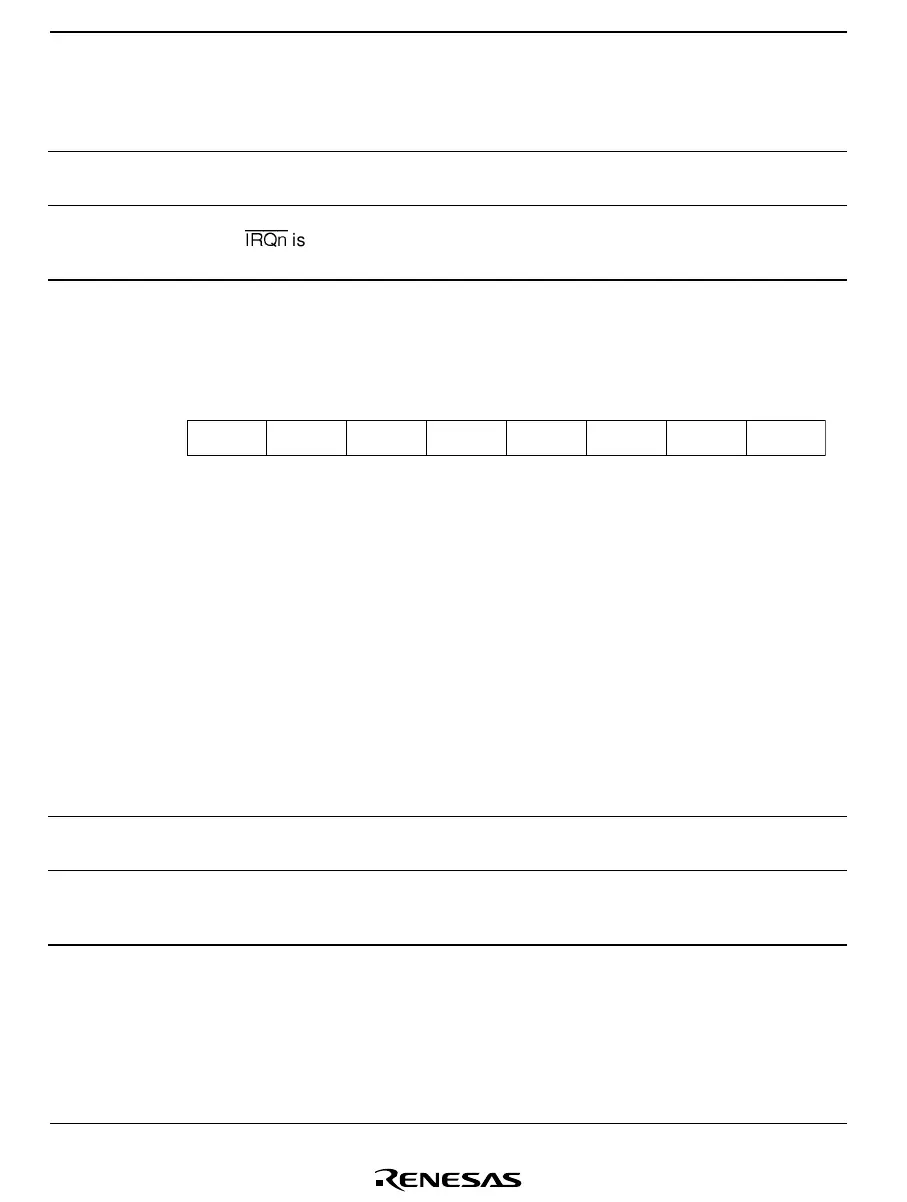

Interrupt Request Register 2 (IRR2)

Bit

Initial value

Read/Write

7

IRRDT

0

R/(W)

*

6

IRRAD

0

R/(W)

*

5

W

4

IRRTG

0

R/(W)

*

3

IRRTFH

0

R/(W)

*

0

IRREC

0

R/(W)

*

2

IRRTFL

0

R/(W)

*

1

IRRTC

0

R/(W)

*

Note: * Only a write of 0 for flag clearing is possible

IRR2 is an 8-bit read/write register, in which a corresponding flag is set to 1 when a direct

transfer, A/D converter, Timer G, Timer FH, Timer FL, Timer C, or asynchronous event counter

interrupt is requested. The flags are not cleared automatically when an interrupt is accepted. It is

necessary to write 0 to clear each flag.

Bit 7—Direct Transfer Interrupt Request Flag (IRRDT)

Bit 7

IRRDT Description

0

Clearing conditions: (initial value)

When IRRDT = 1, it is cleared by writing 0

1

Setting conditions:

When a direct transfer is made by executing a SLEEP instruction while DTON = 1 in

SYSCR2

Loading...

Loading...