Rev. 7.00 Mar 10, 2005 page xx of xlii

Item Page Revision (See Manual for Details)

10.3.3 Operation in

Synchronous Mode

• Receiving

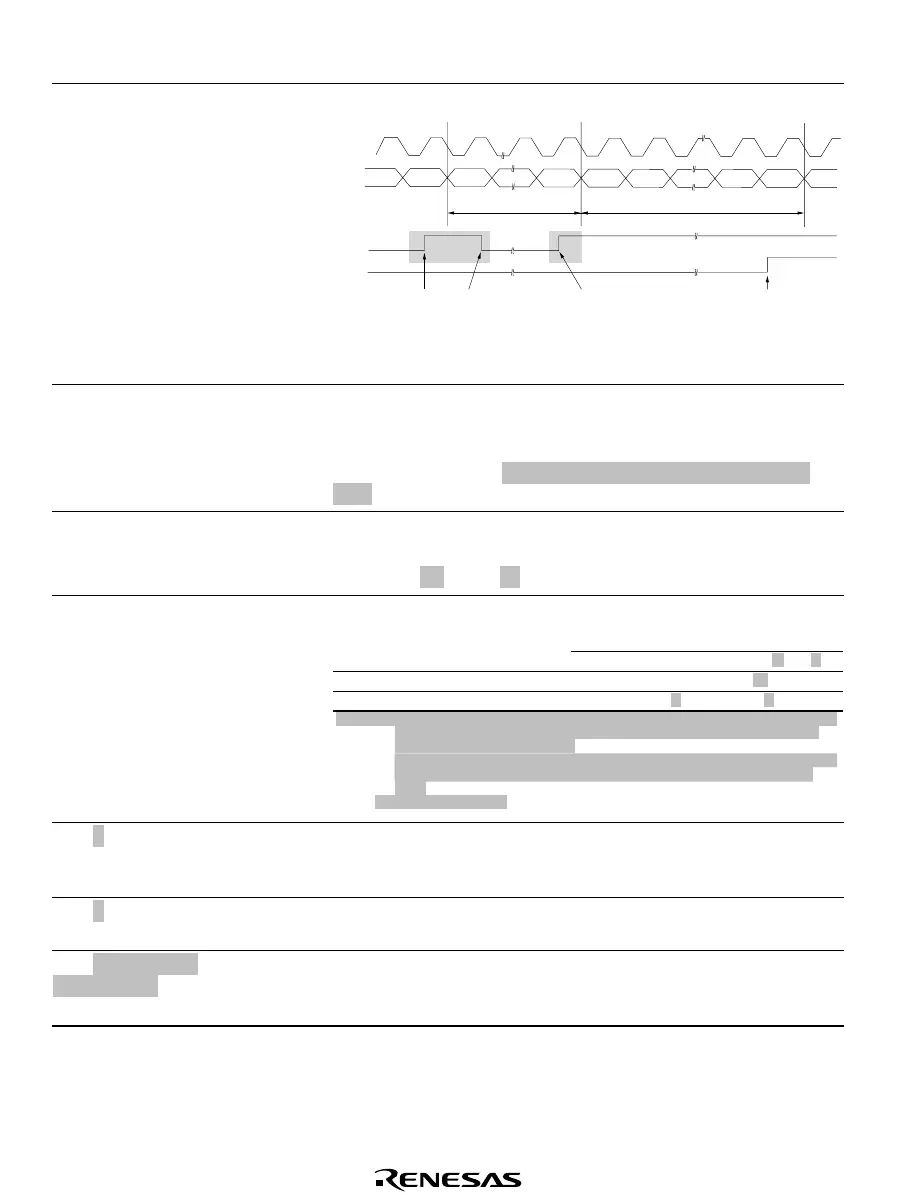

Figure 10.14

Example of Operation

when Receiving in

Synchronous Mode

374 Figure amended

Serial

clock

Serial

data

Bit 0Bit 7 Bit 7 Bit 0

1 frame 1 frame

Bit 1 Bit 6 Bit 7

RDRF

OER

LSI

operation

User

processing

RXI request

RDR data read

RDRE cleared

to 0

RXI request ERI request in

response to

overrun error

Overrun error

processing

RDR data has

not been read

(RDRF = 1)

11.3.1 Operation 396 Description amended

1. Set PWM1 or PWM2 in PMR9 to 1 for the PWM channel to

be used, so that pin P9

0

/PWM1 or P9

1

/PWM2 is designated as

the PWM output pin, or both are designated as PWM output

pins.

12.1.1 Features 399 Description amended

• Conversion time: approx. 12.4 µs per channel (at 5 MHz

operation)/6.2 µs (at 10 MHz operation)*

12.2.2 A/D Mode

Register (AMR)

Bit 7—Clock Select

(CKS)

403 Bit table and notes amended

Conversion Time

Bit 7

CKS

Conversion Period φ

φφ

φ = 1 MHz φ

φφ

φ = 5 MHz φ

φφ

φ =

10 MHz

*

2

0 62/φ (initial value) 62 µs 12.4 µs 6.2 µs

1 31/φ 31 µs —

*

1

—

*

1

Notes: 1. With the H8/38024, H8/38024S, and H8/38024F-ZTAT operation cannot be guaranteed

if the conversion time is less than 12.4 µs. Make sure to select a setting that gives a

conversion time of 12.4

With the H8/38124 Group operation cannot be guaranteed if the conversion time is less

than 6.2 µs. Make sure to select a setting that gives a conversion time of 6.2 µs or

more.

µs or more.

2. H8/38124 Group only.

12.7.1 Permissible

Signal Source

Impedance

413 Title amended

12.7.2 Influences on

Absolute Precision

413 Title amended

12.7.3 Additional

Usage Notes

414 Title amended

Loading...

Loading...