Section 9 Timers

Rev. 7.00 Mar 10, 2005 page 268 of 652

REJ09B0042-0700

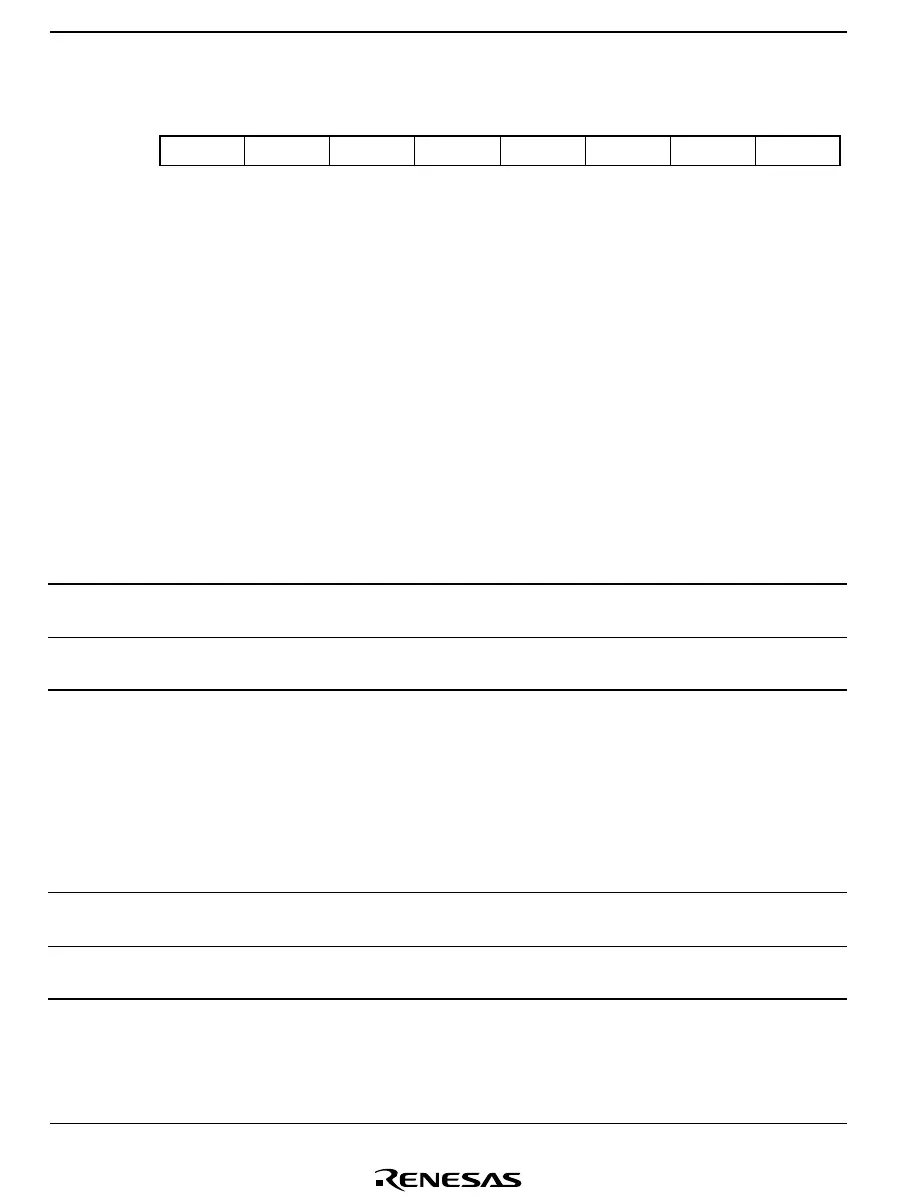

Timer Control/Status Register F (TCSRF)

OVFH CMFL OVIEL CCLRLCMFH OVIEH CCLRH OVFL

76543210

0

0000000

R/(W)

*

R/(W)

*

R/W R/W

R/(W)

*

R/W R/W

R/(W)

*

Note: * Bits 7, 6, 3, and 2 can only be written with 0, for flag clearing.

Bit:

Initial value:

Read/Write:

TCSRF is an 8-bit read/write register that performs counter clear selection, overflow flag setting,

and compare match flag setting, and controls enabling of overflow interrupt requests.

TCSRF is initialized to H'00 upon reset.

Bit 7—Timer Overflow Flag H (OVFH)

Bit 7 is a status flag indicating that TCFH has overflowed from H'FF to H'00. This flag is set by

hardware and cleared by software. It cannot be set by software.

Bit 7

OVFH Description

0 Clearing condition: (initial value)

After reading OVFH = 1, cleared by writing 0 to OVFH

1 Setting condition:

Set when TCFH overflows from H’FF to H’00

Bit 6—Compare Match Flag H (CMFH)

Bit 6 is a status flag indicating that TCFH has matched OCRFH. This flag is set by hardware and

cleared by software. It cannot be set by software.

Bit 6

CMFH Description

0 Clearing condition: (initial value)

After reading CMFH = 1, cleared by writing 0 to CMFH

1 Setting condition:

Set when the TCFH value matches the OCRFH value

Loading...

Loading...