Section 9 Timers

Rev. 7.00 Mar 10, 2005 page 317 of 652

REJ09B0042-0700

Bit 1—Event Counter PWM Enable

Bit 1 controls enabling/disabling of event counter PWM and selection/deselection of IRQAEC.

Bit 1

ECPWME Description

0 AEC PWM halted, IRQAEC selected (initial value)

1 AEC PWM operation enabled, IRQAEC deselected

Bit 0—Reserved

Bit 0 is a readable/writable reserved bit. It is initialized to 0 by a reset.

Note: Do not set this bit to 1.

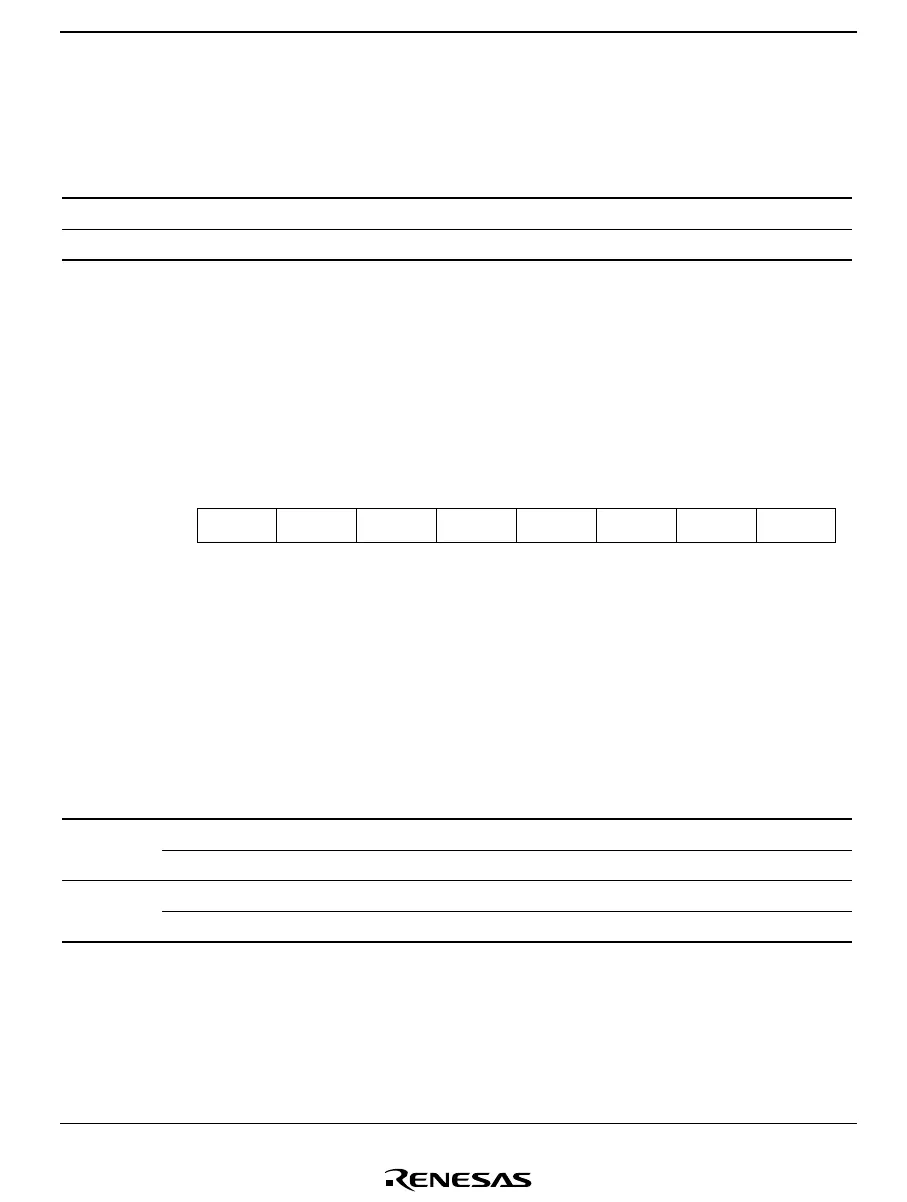

Event Counter Control Register (ECCR)

Bit

Initial value

Read/Write

7

ACKH1

0

R/W

6

ACKH0

0

R/W

5

ACKL1

0

R/W

4

ACKL0

0

R/W

3

PWCK2

0

R/W

0

0

R/W

2

PWCK1

0

R/W

1

PWCK0

0

R/W

ECCR performs counter input clock and IRQAEC/IECPWM control.

Bits 7 and 6—AEC Clock Select H (ACKH1, ACKH0)

Bits 7 and 6 select the clock used by ECH.

Bit 7

ACKH1

Bit 6

ACKH0 Description

0 0 AEVH pin input (initial value)

1 φ/2

10φ/4

1 φ/8

Loading...

Loading...