Section 9 Timers

Rev. 7.00 Mar 10, 2005 page 326 of 652

REJ09B0042-0700

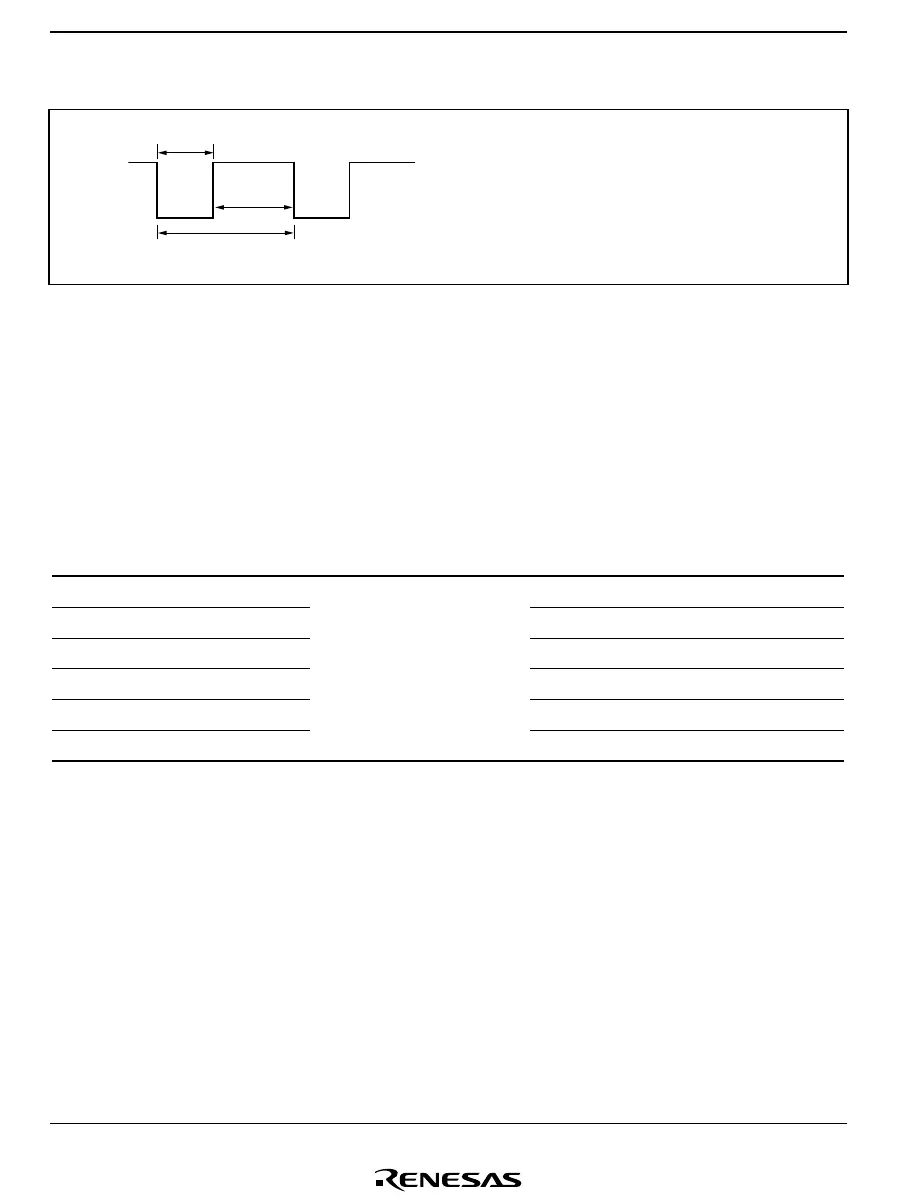

Figure 9.22 and table 9.20 show examples of event counter PWM operation.

toff = T × (Ndr +1)

t

on

tcm = T × (Ncm +1)

T

on

: Clock input enabled time

T

off

: Clock input disabled time

T

cm

: One conversion period

T : ECPWM input clock cycle

N

dr

: Value of ECPWDRH and ECPWDRL

Fixed low when Ndr = H'FFFF

N

cm

: Value of ECPWCRH and ECPWCRL

Figure 9.22 Event Counter Operation Waveform

Note: N

dr

and N

cm

above must be set so that N

dr

< N

cm

. If the settings do not satisfy this

condition, do not set ECPWME in AEGSR to 1.

Table 9.20 Examples of Event Counter PWM Operation

Conditions: f

osc

= 4 MHz, f

φ

= 2 MHz, high-speed active mode, ECPWCR value (N

cm

) = H'7A11,

ECPWDR value (N

dr

) = H'16E3

Clock Source

Selection

Clock Source

Cycle (T)

*

ECPWCR

Value (N

cm

)

ECPWDR

Value (N

dr

)

t

off

= T •

(N

dr

+ 1)

t

cm

= T •

(N

cm

+ 1) t

on

= t

cm

– t

off

φ/2 1 µs 5.86 ms 31.25 ms 25.39 ms

φ/4 2 µs

H'7A11

D'31249

H'16E3

D'5859

11.72 ms 62.5 ms 50.78 ms

φ/8 4 µs 23.44 ms 125.0 ms 101.56 ms

φ/16 8 µs 46.88 ms 250.0 ms 203.12 ms

φ/32 16 µs 93.76 ms 500.0 ms 406.24 ms

φ/64 32 µs 187.52 ms 1000.0 ms 812.48 ms

Note: * t

off

minimum width

Loading...

Loading...