Section 10 Serial Communication Interface

Rev. 7.00 Mar 10, 2005 page 353 of 652

REJ09B0042-0700

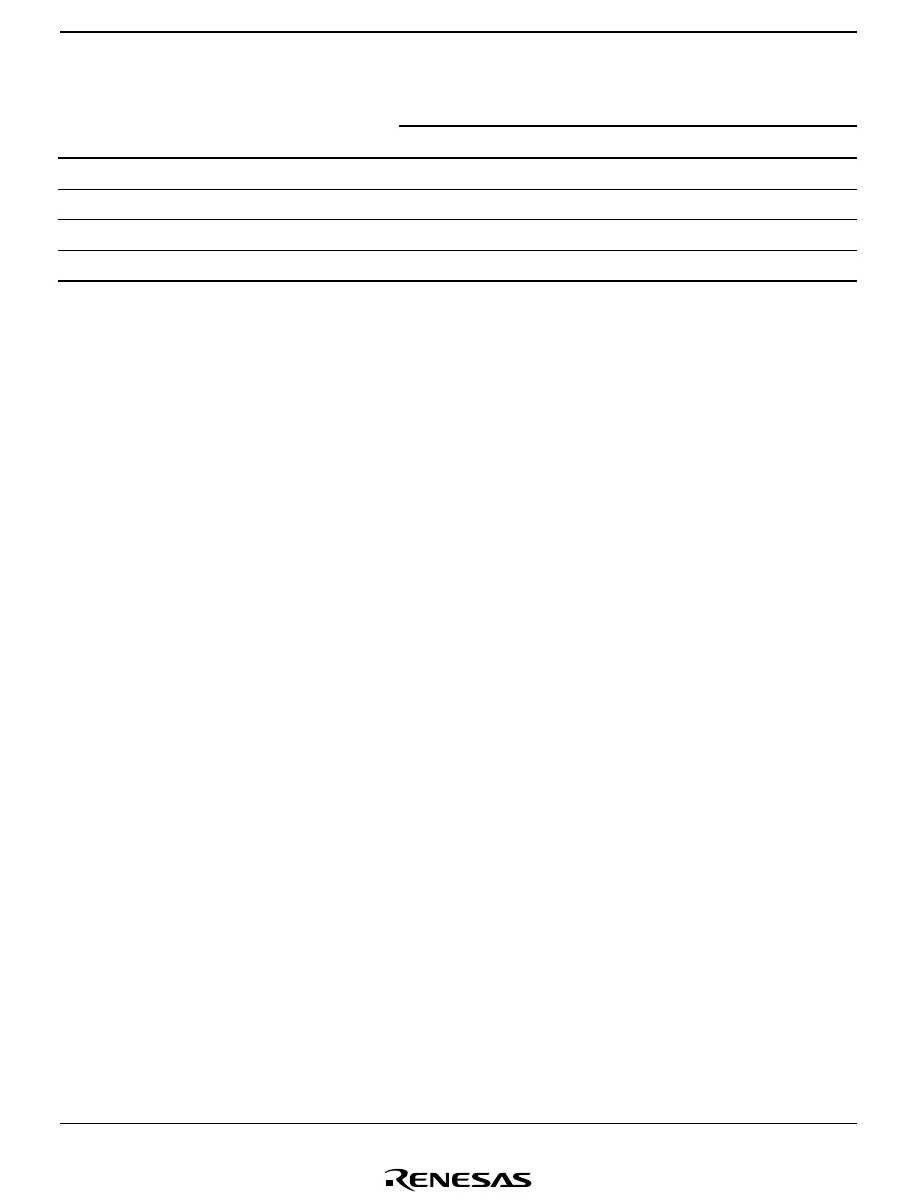

Table 10.7 Relation between n and Clock

SMR Setting

n Clock CKS1 CKS0

0 φ 00

0 φ

w

/2

*

1

/φw

*

2

01

2 φ/16 1 0

3 φ/64 1 1

Notes: 1. φw/2 clock in active (medium-speed/high-speed) mode and sleep mode

2. φw clock in subactive mode and subsleep mode

In subactive or subsleep mode, SCI3 can be operated when CPU clock is φw/2 only.

Loading...

Loading...