Appendix B Internal I/O Registers

Rev. 7.00 Mar 10, 2005 page 582 of 652

REJ09B0042-0700

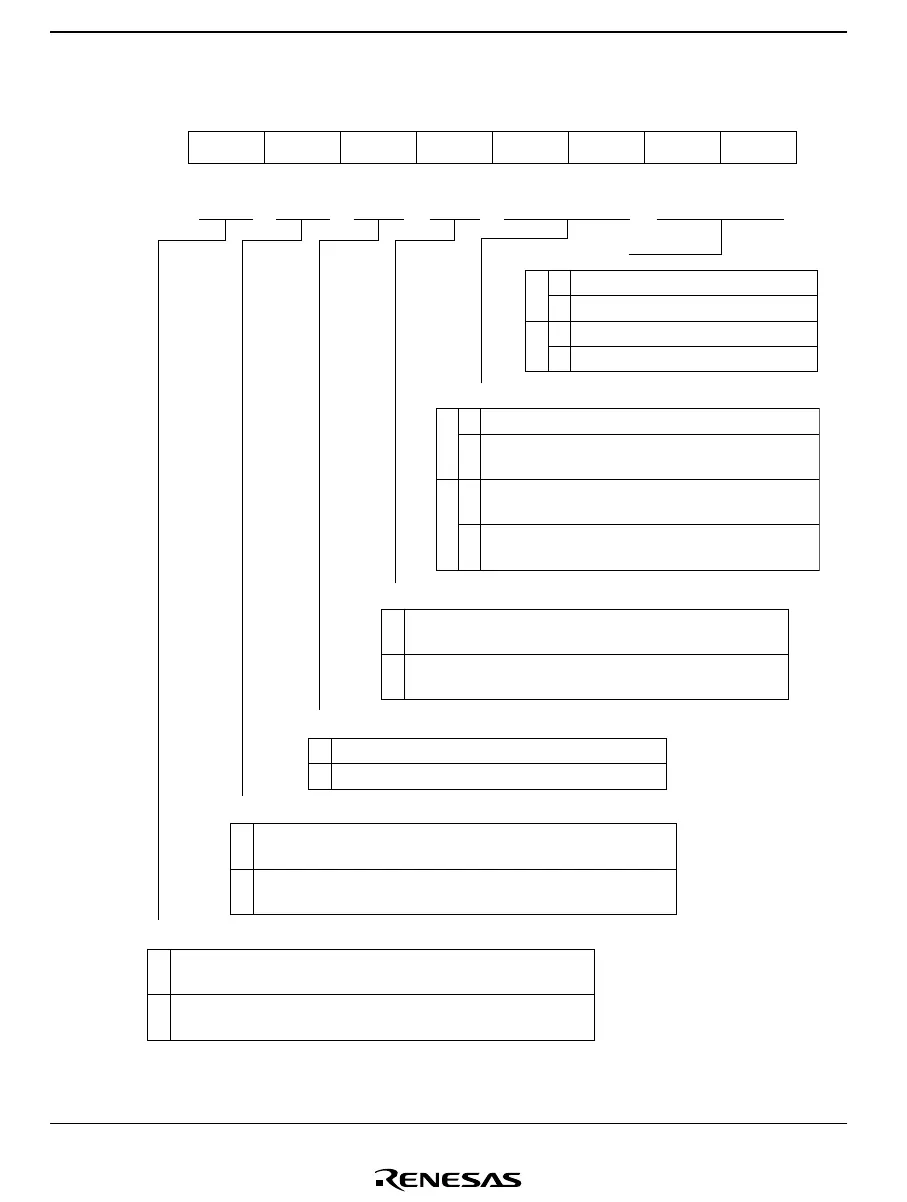

TMG—Timer Mode Register G H'BC Timer G

Bit

Initial value

Read/Write

7

OVFH

0

R/(W)

*

6

OVFL

0

R/(W)

*

5

OVIE

0

R/W

3

CCLR1

0

R/W

0

CKS0

0

R/W

2

CCLR0

0

R/W

1

CKS1

0

R/W

4

IIEGS

0

R/W

Timer Overflow Flag L

0 Clearing condition:

After reading OVFL = 1, cleared by writing 0 to OVFL

1 Setting condition:

Set when TCG overflows from H'FF to H'00

Timer Overflow Flag H

0 Clearing condition:

After reading OVFH = 1, cleared by writing 0 to OVFH

1 Setting condition:

Set when TCG overflows from H'FF to H'00

Input Capture Interrupt Edge Select

0 Interrupt generated on rising edge of input capture

input signal

1 Interrupt generated on falling edge of input capture

input signal

Timer Overflow Interrupt Enable

0 TCG overflow interrupt request is disabled

1 TCG overflow interrupt request is enabled

Clock Select

0 Internal clock: counting on φ/64

0

1 Internal clock: counting on φ/32

1 0 Internal clock: counting on φ/2

1 Internal clock: counting on φ

W

/4

Counter Clear

0 TCG clearing is disabled

0

1 TCG cleared by falling edge of input capture

input signal

1 0 TCG cleared by rising edge of input capture

input signal

1 TCG cleared by both edges of input capture

input signal

Note: * Bits 7 and 6 can only be written with 0, for flag clearing.

Loading...

Loading...