Appendix B Internal I/O Registers

Rev. 7.00 Mar 10, 2005 page 605 of 652

REJ09B0042-0700

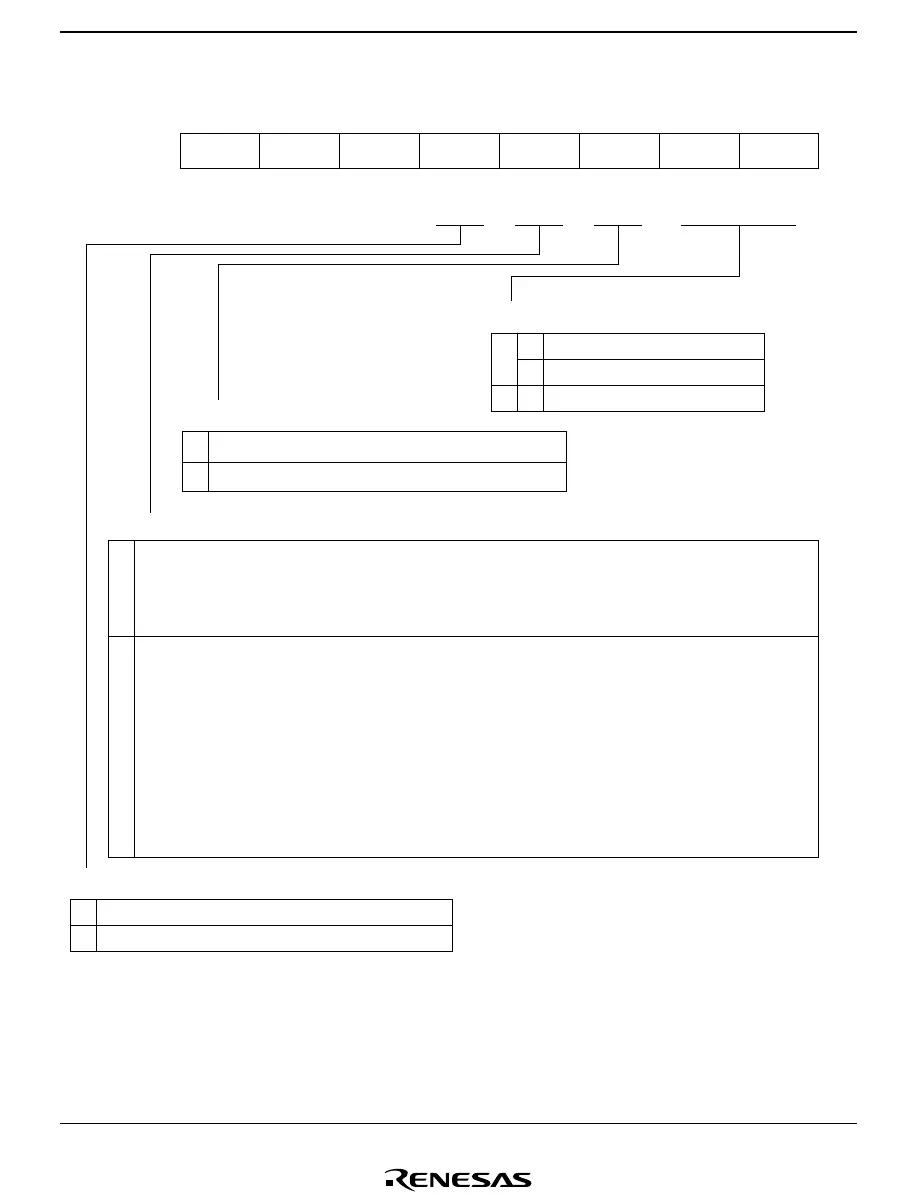

SYSCR2—System Control Register 2 H'F1 System Control

Bit

Initial value

Read/Write

7

1

6

1

5

1

3

DTON

0

R/W

0

SA0

0

R/W

2

MSON

0

R/W

1

SA1

0

R/W

4

NESEL

1

R/W

Subactive Mode Clock Select

0 φ

W

/8

φ

W

/4

0

1

1 φ

W

/2

*

Direct Transfer on Flag

0 • When a SLEEP instruction is executed in active mode, a transition is

made to standby mode, watch mode, or sleep mode

1

• When a SLEEP instruction is executed in subactive mode, a transition is

made to watch mode or subsleep mode

• When a SLEEP instruction is executed in active (high-speed) mode, a direct

transition is made to active (medium-speed) mode if SSBY = 0, MSON = 1, and

LSON = 0, or to subactive mode if SSBY = 1, TMA3 = 1, and LSON = 1

• When a SLEEP instruction is executed in active (medium-speed) mode, a direct

transition is made to active (high-speed) mode if SSBY = 0, MSON = 0, and

LSON = 0, or to subactive mode if SSBY = 1, TMA3 = 1, and LSON = 1

• When a SLEEP instruction is executed in subactive mode, a direct

transition is made to active (high-speed) mode if SSBY = 1, TMA3 = 1, LSON = 0,

and MSON = 0, or to active (medium-speed) mode if SSBY = 1, TMA3 = 1,

LSON = 0, and MSON = 1

Medium Speed on Flag

0 Operates in active (high-speed) mode

1 Operates in active (medium-speed) mode

Noise Elimination Sampling Frequency Select

0 Sampling rate is φ

OSC

/16

1 Sampling rate is φ

OSC

/4

*: Don't care

Loading...

Loading...