119

3) Suitable soft components

*Notes: D includes D, HD; TD includes TD, HTD; CD includes CD, HCD, HSCD, HSD; DM

includes DM, DHM; DS includes DS, DHS. M includes M,HM,SM;S includes S,HS;T

includes T,HT;C includes C, HC.

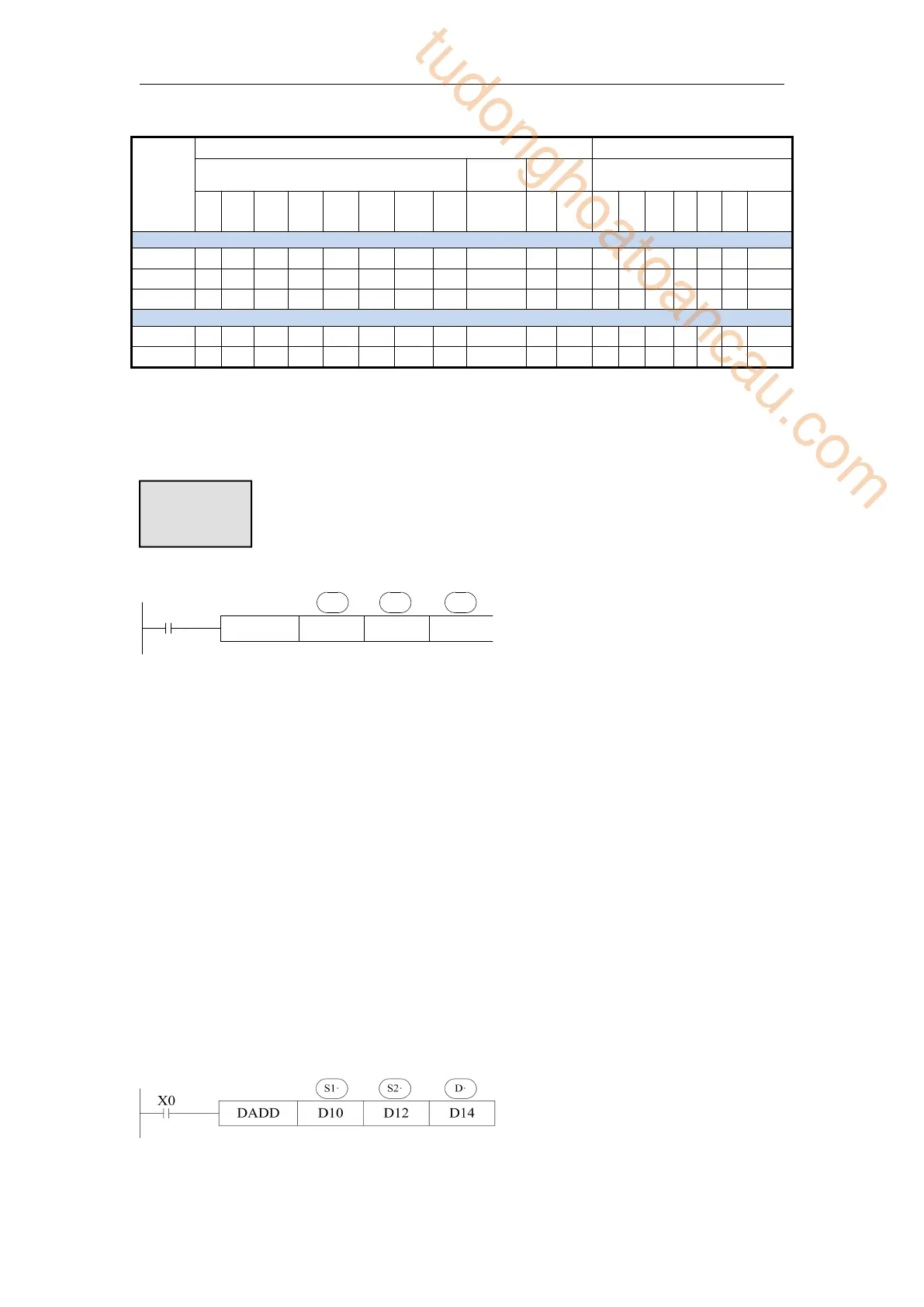

<Three operands>

ADD D10 D12 D14

X0

S1· S2· D·

Two source data do binary addition and send the result to target address. Each data’s highest

bit is the sign bit, 0 stands for positive, 1 stands for negative. All calculations are algebraic

processed. (5+ (-8) =-3)

If the result of a calculation is “0”, the “0” flag acts. If the result exceeds 323767 (16 bits

operation) or 2147483647 (32 bits operation) or 9223372036854775807(64 bits operation),

the carry flag acts (refer to the Related flag). If the result exceeds –323768(16 bits

operation)or –2147483648 (32 bits operation) or -9223372036854775808(64 bits operation),

the borrow flag acts (refer to the Related flag).

When doing 32/64 bits operation, the lower 16-bit side of the word soft component is

specified, and the next numbered soft component will be used as the high position. To avoid

ID repetition, it is recommended that the soft component be specified with an even number.

For example, the 32-bit notation of the preceding example is shown in the following figure.

In 32-bit operation, the address of the second addend must start from D12 because the first

addend occupies registers D10 and D11. To avoid registers being occupied repeatedly, it is

recommended that the soft components be numbered as even numbers.

(D11

,

D10)

+

(D13

,

D12)

→

(D15

,

D14)

tudonghoatoancau.com

Loading...

Loading...