112©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

ALERT_CFG.IN9_8_MON_ALERT_MASK

GPIO alert enable masks (frequency offset, no activity, loss of signal) for reference monitors 8 and 9.

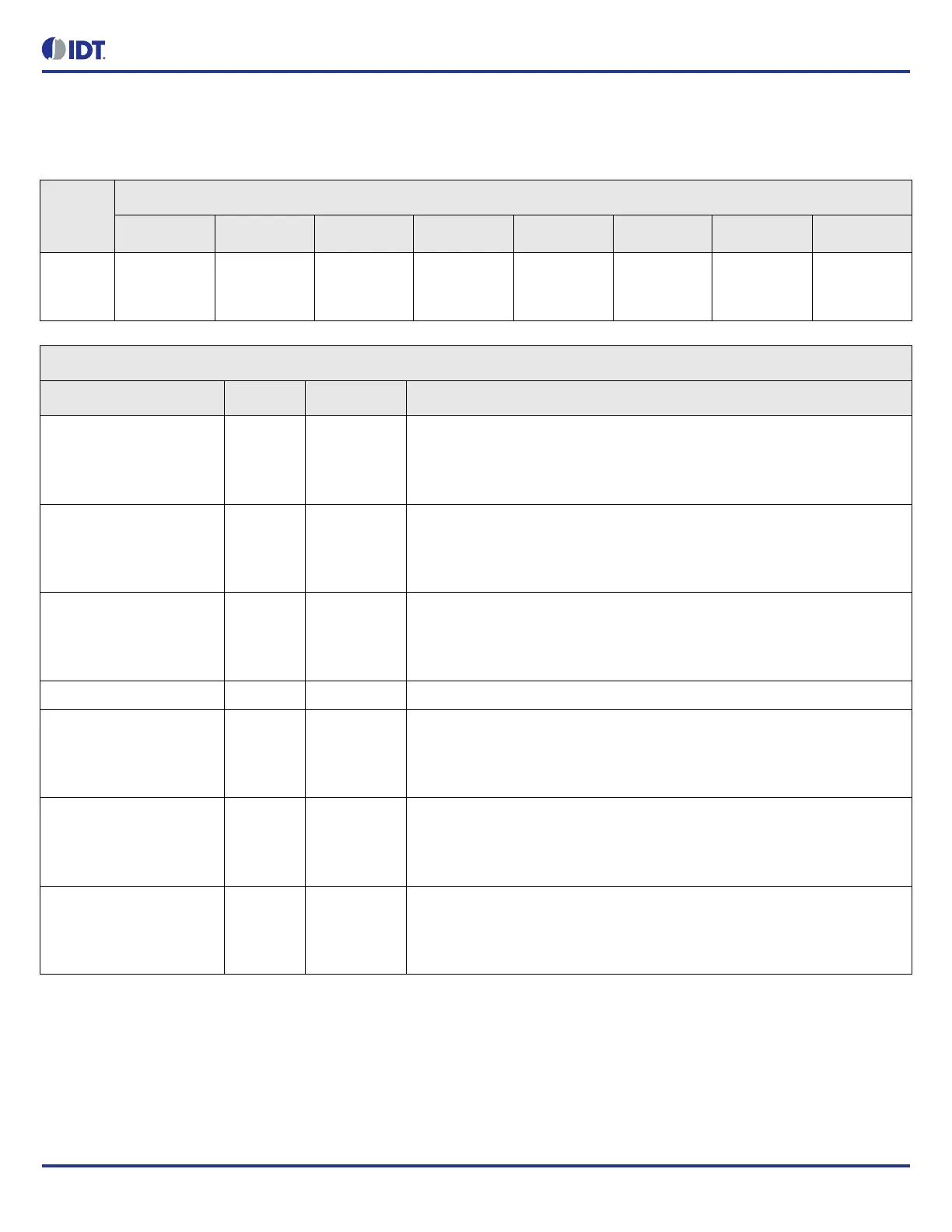

Table 137: ALERT_CFG.IN9_8_MON_ALERT_MASK Bit Field Locations and Descriptions

Offset

Address

(Hex)

ALERT_CFG.IN9_8_MON_ALERT_MASK Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

004h RESERVED[

7]

IN9_FREQ_

OFFS_LIM_

MASK[6]

IN9_NO_AC

TIVITY_MAS

K[5]

IN9_LOS_M

ASK[4]

RESERVED[

3]

IN8_FREQ_

OFFS_LIM_

MASK[2]

IN8_NO_AC

TIVITY_MAS

K[1]

IN8_LOS_M

ASK[0]

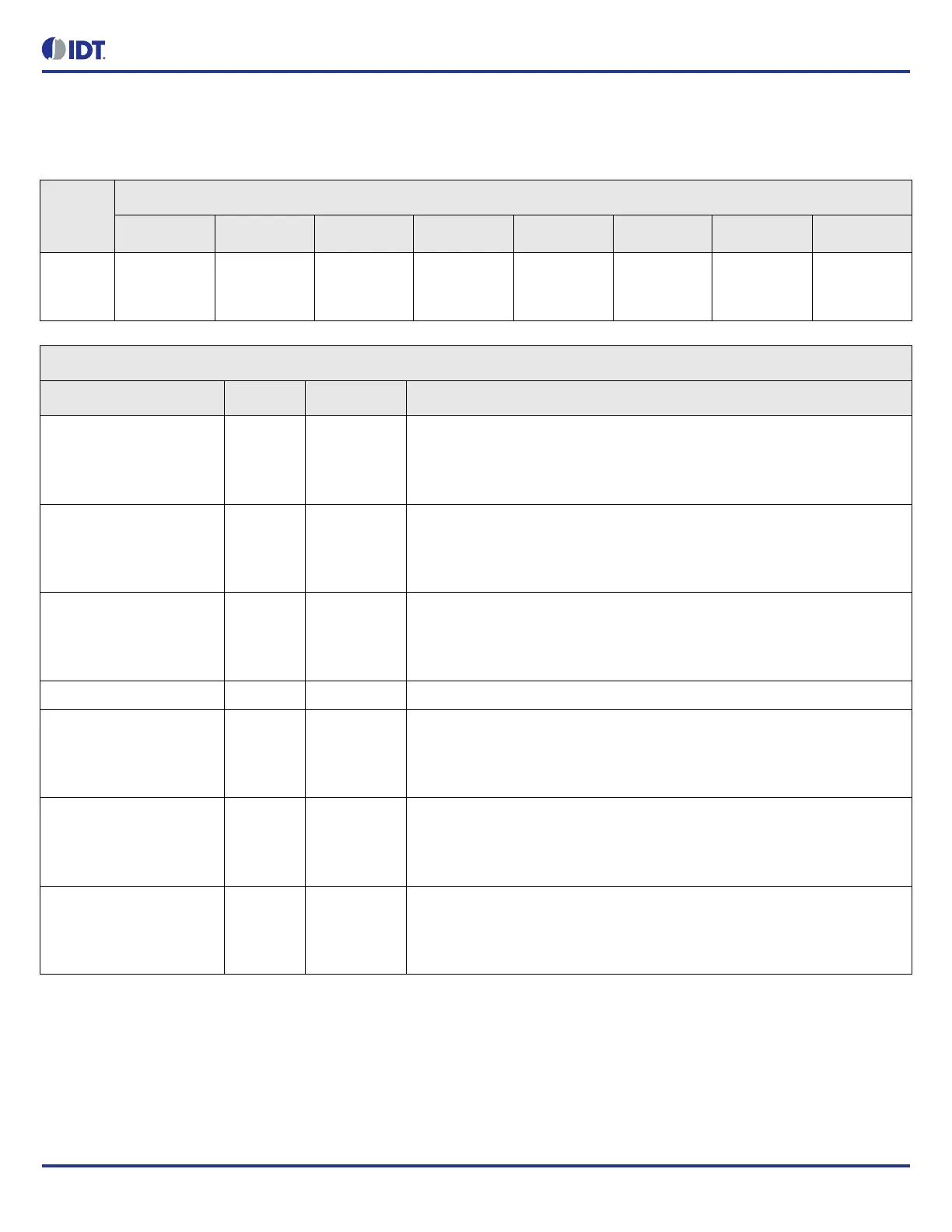

ALERT_CFG.IN9_8_MON_ALERT_MASK Bit Field Descriptions

Bit Field Name Field Type Default Value Description

IN9_FREQ_OFFS_LIM_M

ASK[6]

R/W 0 Input 9 frequency offset limit enable mask.

If enabled, GPIO alert becomes active when in9_freq_offs_lim_sticky bit is set.

0 = disabled

1 = enabled

IN9_NO_ACTIVITY_MASK

[5]

R/W 0 Input 9 no activity enable mask.

If enabled, GPIO alert becomes active when in9_no_activity_sticky bit is set.

0 = disabled

1 = enabled

IN9_LOS_MASK[4] R/W 0 Input 9 LOS enable mask.

If enabled, GPIO alert becomes active when in9_los_sticky bit is set.

0 = disabled

1 = enabled

RESERVED N/A - This field must not be modified from the read value

IN8_FREQ_OFFS_LIM_M

ASK[2]

R/W 0 Input 8 frequency offset limit enable mask.

If enabled, GPIO alert becomes active when in8_freq_offs_lim_sticky bit is set.

0 = disabled

1 = enabled

IN8_NO_ACTIVITY_MASK

[1]

R/W 0 Input 8 no activity enable mask.

If enabled, GPIO alert becomes active when in8_no_activity_sticky bit is set.

0 = disabled

1 = enabled

IN8_LOS_MASK[0] R/W 0 Input 8 LOS enable mask.

If enabled, GPIO alert becomes active when in08_los_sticky bit is set.

0 = disabled

1 = enabled

Loading...

Loading...