84©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

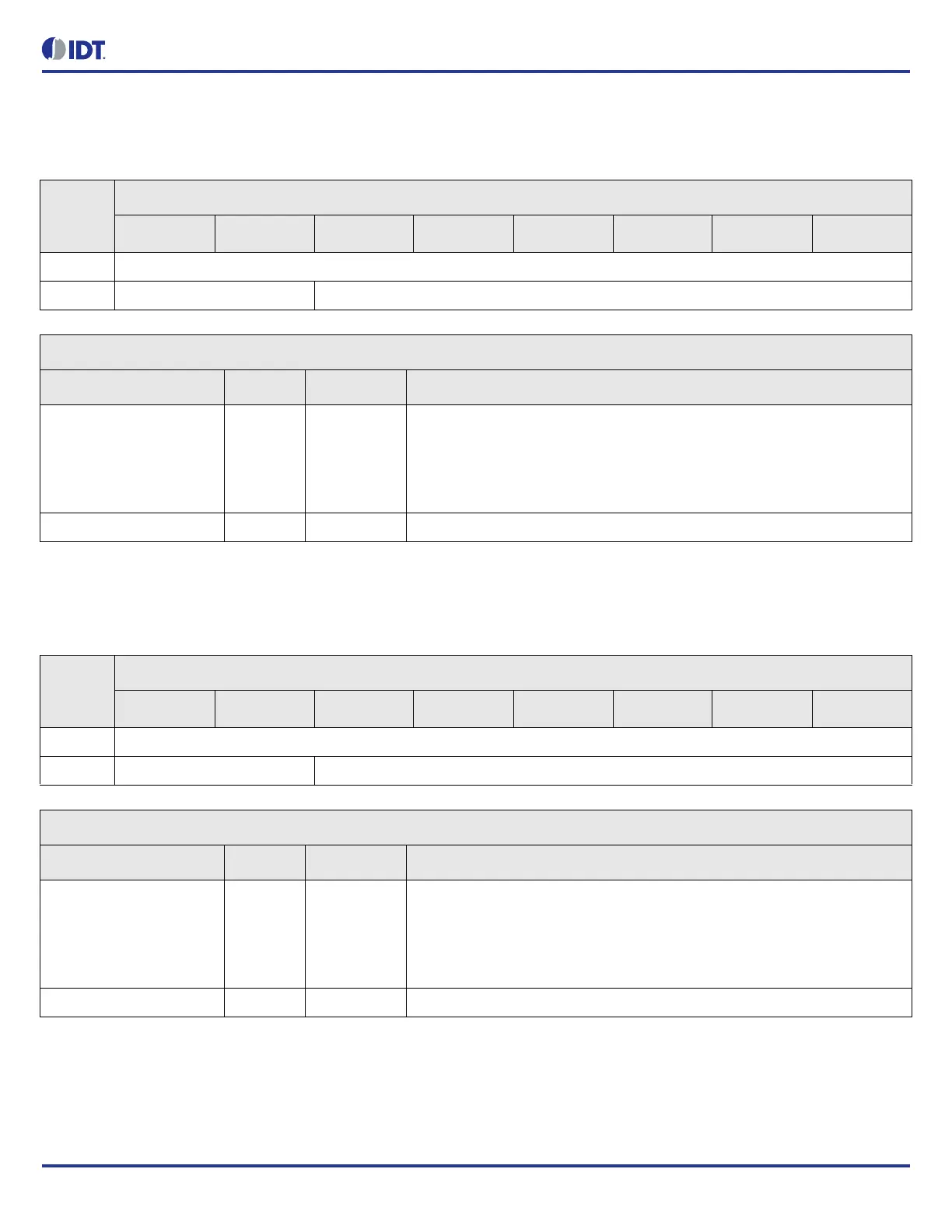

STATUS.IN14_MON_FREQ_STATUS

Input 14 reference monitor frequency status and unit.

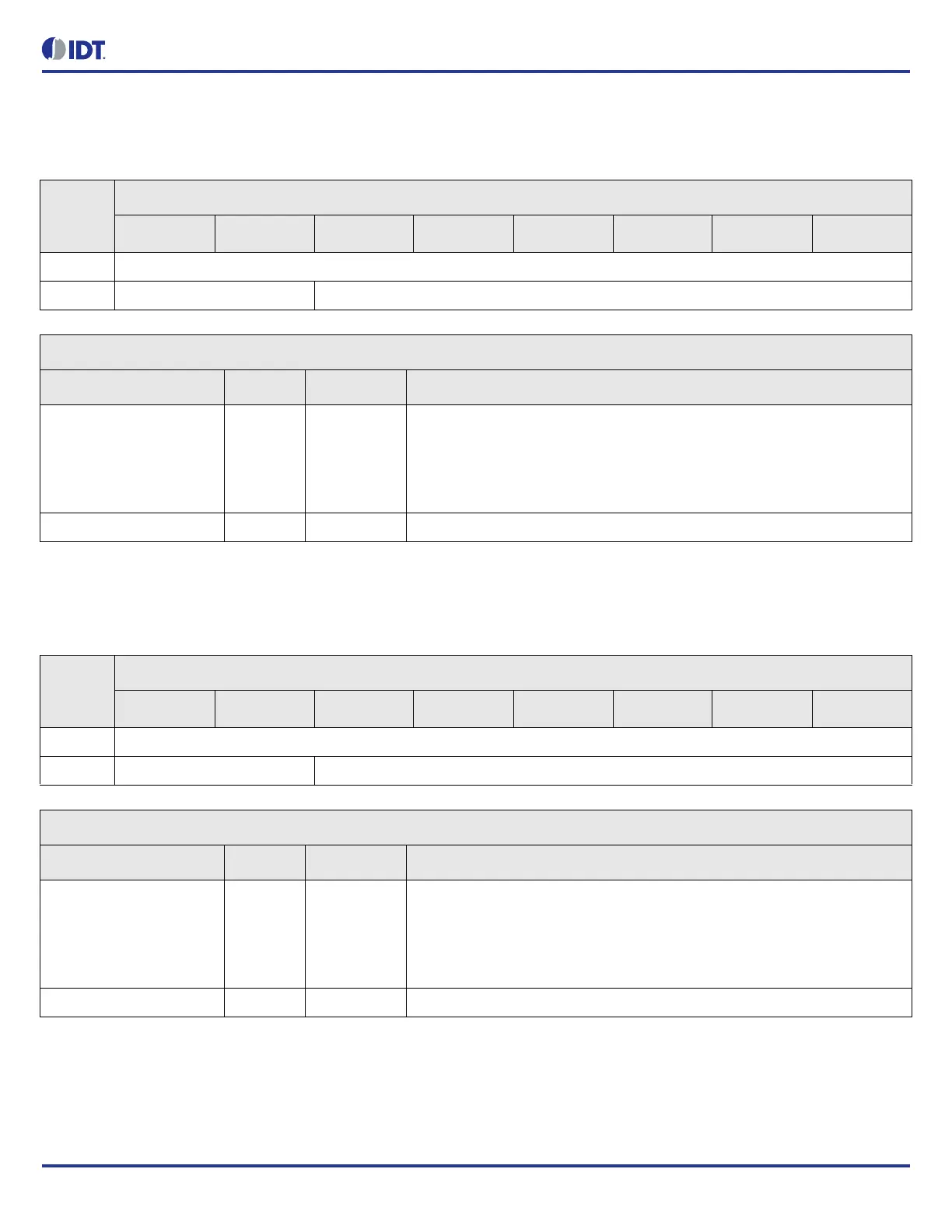

STATUS.IN15_MON_FREQ_STATUS

Input 15 reference monitor frequency status and unit.

Table 92: STATUS.IN14_MON_FREQ_STATUS Bit Field Locations and Descriptions

Offset

Address

(Hex)

STATUS.IN14_MON_FREQ_STATUS Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

0A8h FFO[7:0]

0A9h FFO_UNIT[15:14] FFO[13:8]

STATUS.IN14_MON_FREQ_STATUS Bit Field Descriptions

Bit Field Name Field Type Default Value Description

FFO_UNIT[15:14] R/O 0 Input clock FFO unit enumeration.

0 = 1 ppb

1 = 10 ppb

2 = 100 ppb

3 = 1 ppm

FFO[13:0] R/O 0 Signed 14-bit input clock fractional frequency offset.

Table 93: STATUS.IN15_MON_FREQ_STATUS Bit Field Locations and Descriptions

Offset

Address

(Hex)

STATUS.IN15_MON_FREQ_STATUS Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

0AAh FFO[7:0]

0ABh FFO_UNIT[15:14] FFO[13:8]

STATUS.IN15_MON_FREQ_STATUS Bit Field Descriptions

Bit Field Name Field Type Default Value Description

FFO_UNIT[15:14] R/O 0 Input clock FFO unit enumeration.

0 = 1 ppb

1 = 10 ppb

2 = 100 ppb

3 = 1 ppm

FFO[13:0] R/O 0 Signed 14-bit input clock fractional frequency offset.

Loading...

Loading...