22©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

RESET_CTRL.SM_RESET

Enable state machine reset.

TRIGGER: Writing to this byte triggers a read and activation in hardware of all the bytes of the RESET_CTRL module.

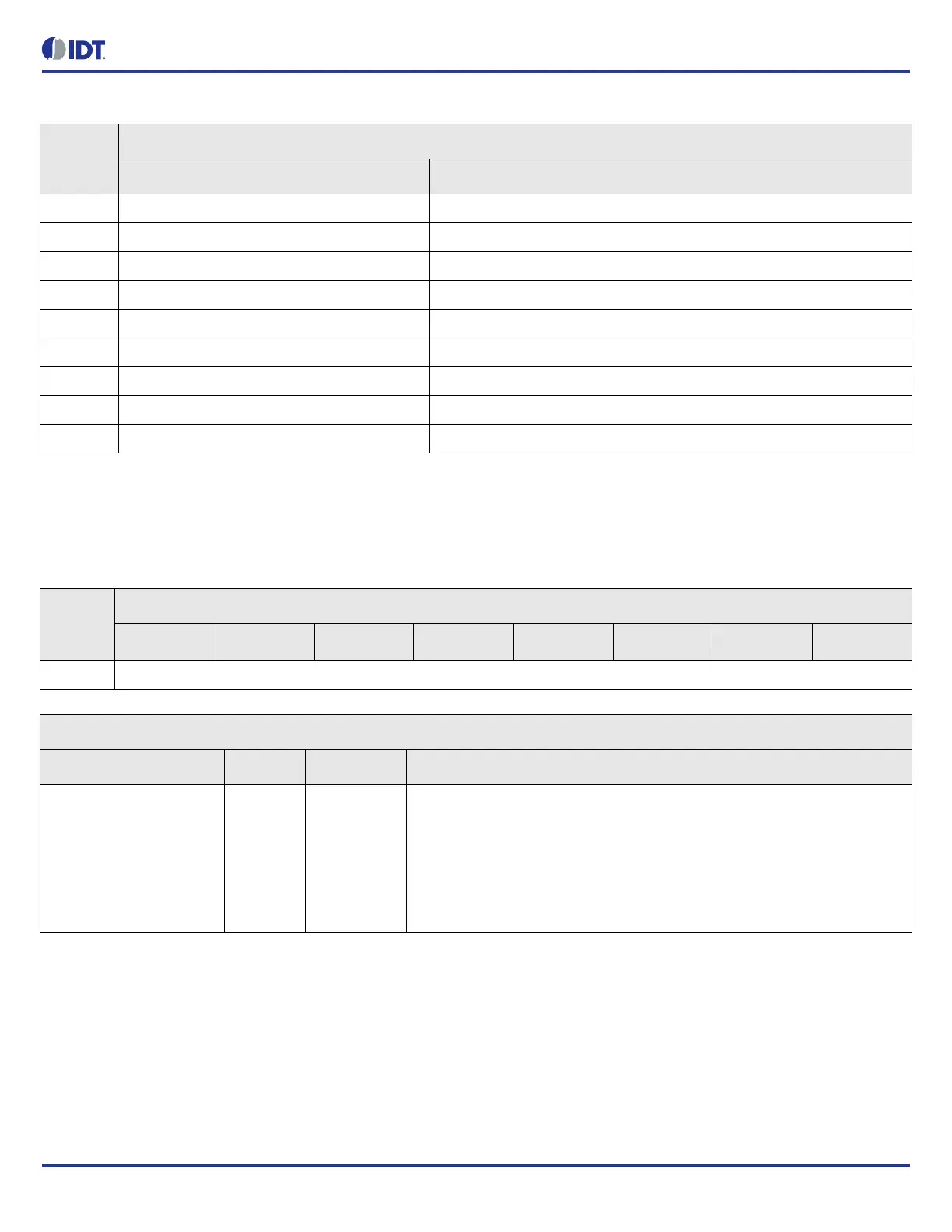

00Ah RESERVED This register must not be modified from the read value

00Bh RESERVED This register must not be modified from the read value

00Ch RESERVED This register must not be modified from the read value

00Dh RESERVED This register must not be modified from the read value

00Eh RESERVED This register must not be modified from the read value

00Fh RESERVED This register must not be modified from the read value

010h RESERVED This register must not be modified from the read value

011h RESERVED This register must not be modified from the read value

012h RESET_CTRL.SM_RESET Reset state machine.

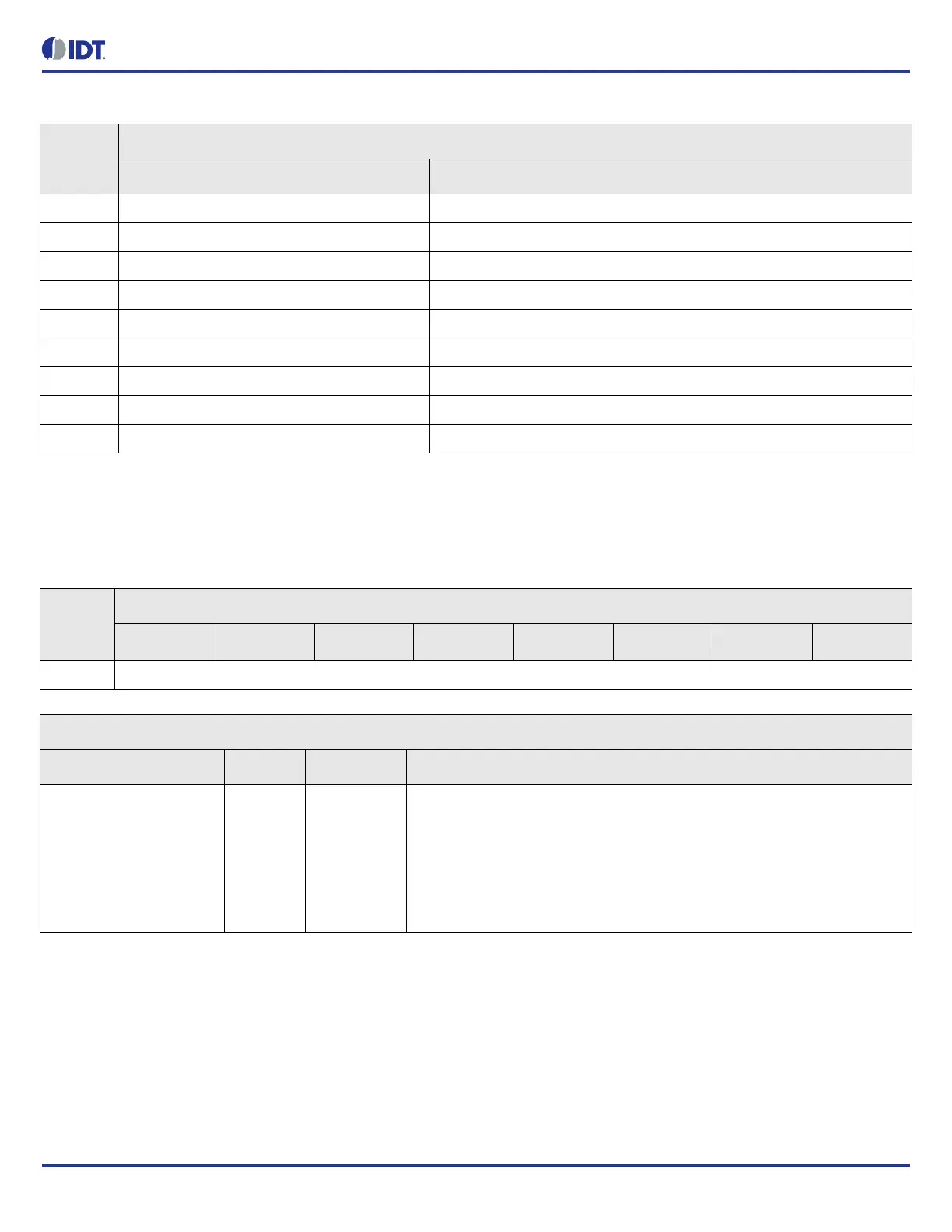

Table 10: RESET_CTRL.SM_RESET Bit Field Locations and Descriptions

Offset

Address

(Hex)

RESET_CTRL.SM_RESET Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

012h RESET[7:0]

RESET_CTRL.SM_RESET Bit Field Descriptions

Bit Field Name Field Type Default Value Description

RESET[7:0] R/W 0 Reset state machine.

0x5a = initiate state machine reset

Write 0x5A to perform state machine reset. All other values are ignored. Self

clearing.

During a state machine reset, all registers starting from GENERAL_STATUS

returns to reset values and the device proceeds with the start-up sequence as if

the device was just powered on. The digital core is not reset.

Table 9: RESET_CTRL Register Index

Offset

(Hex)

Register Module Base Address: C000h

Individual Register Name Register Description

Loading...

Loading...