205©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

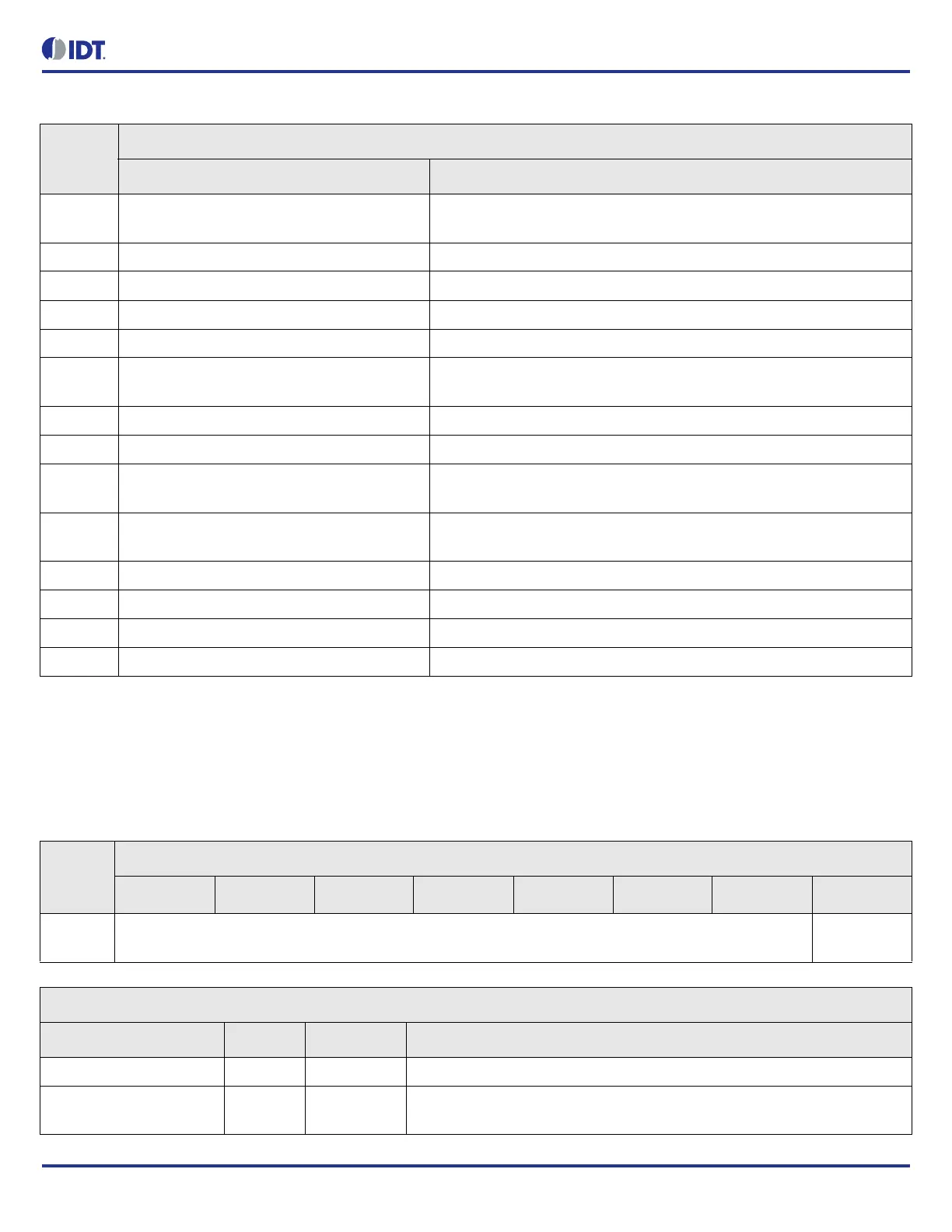

DPLL_CTRL_0.DPLL_HS_TIE_RESET

Reset hitless switching time interval error.

00Fh DPLL_CTRL_0.DPLL_PRED1_DECIMATOR_B

W_MULT

Predefined configuration 1 loop filter decimator bandwidth multiplier.

010h DPLL_CTRL_0.DPLL_PRED1_BW Predefined configuration 1 loop filter bandwidth.

012h DPLL_CTRL_0.DPLL_PRED1_PSL Predefined configuration 1 loop filter phase slope limit.

014h DPLL_CTRL_0.DPLL_PHASE_OFFSET_CFG DPLL phase offset configuration.

019h DPLL_CTRL_0.DPLL_HO_HISTORY_RESET Reset advanced holdover history.

01Ah DPLL_CTRL_0.DPLL_FINE_PHASE_ADV_CF

G

DPLL fine phase advance adjustment configuration.

01Ch DPLL_CTRL_0.DPLL_FOD_FREQ Fractional Output Divider (FOD) frequency in Hz.

024h DPLL_CTRL_0.DPLL_MASTER_DIV Master divider value.

028h DPLL_CTRL_0.DPLL_COMBO_SW_VALUE_C

NFG

DCO value to be added to the combo bus in SW combo mode.

030h DPLL_CTRL_0.DPLL_MANUAL_HOLDOVER_

VALUE

DCO value to be used in manual holdover mode.

036h DPLL_CTRL_0.DPLL_DCD_FILTER_CNFG DPLL DCD filter configuration.

038h DPLL_CTRL_0.DPLL_COMBO_MASTER_BW DPLL combo filter bandwidth.

03Ah DPLL_CTRL_0.DPLL_COMBO_MASTER_CFG DPLL combo master configuration.

03Bh DPLL_CTRL_0.DPLL_FRAME_PULSE_SYNC Frame pulse sync trigger

a. This register module is instantiated multiple times. This is the base address of the first instantiation of this module. For later instantiations,

use the appropriate module base address.

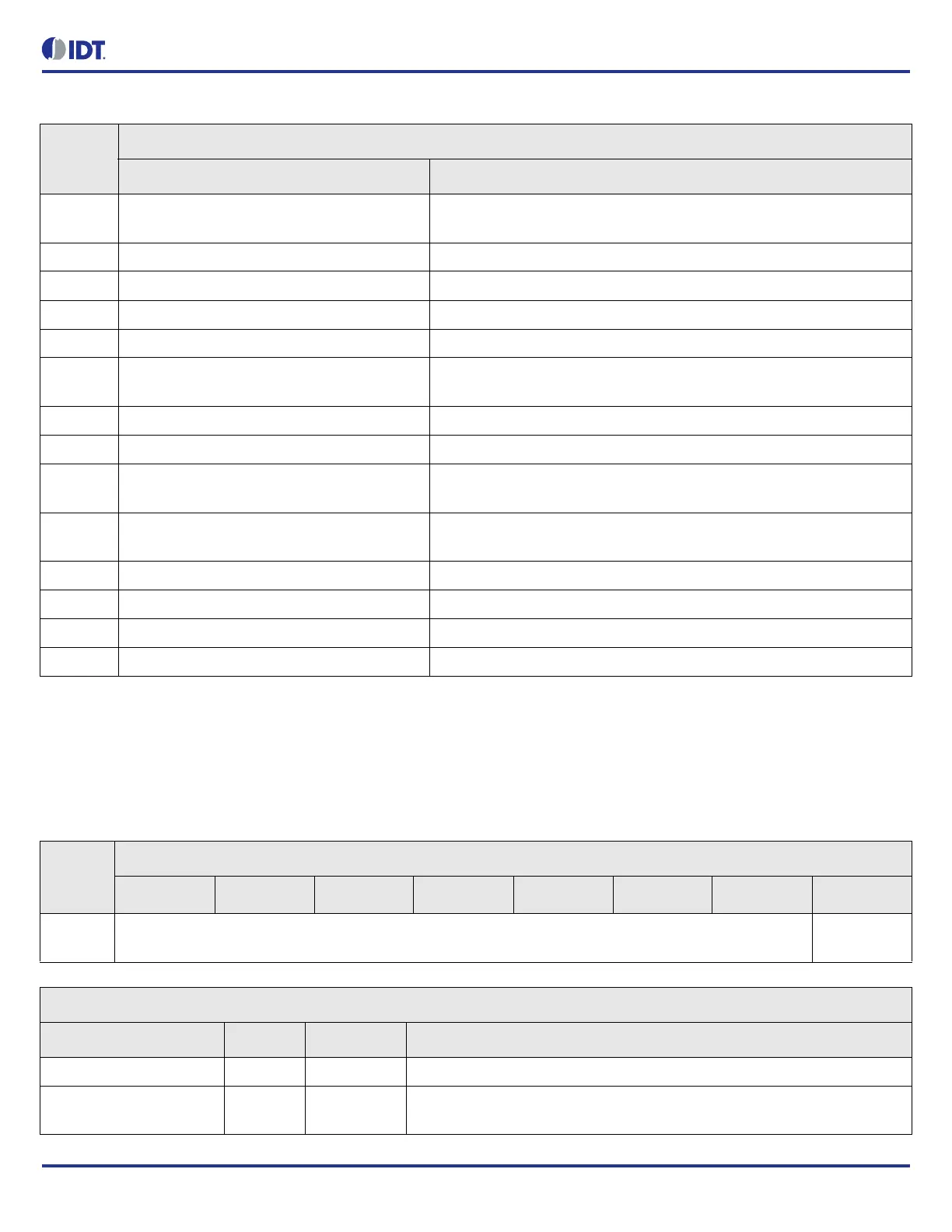

Table 251: DPLL_CTRL_0.DPLL_HS_TIE_RESET Bit Field Locations and Descriptions

Offset

Address

(Hex)

DPLL_CTRL_0.DPLL_HS_TIE_RESET Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

000h RESERVED[7:1] TIE_RESET[

0]

DPLL_CTRL_0.DPLL_HS_TIE_RESET Bit Field Descriptions

Bit Field Name Field Type Default Value Description

RESERVED N/A - This field must not be modified from the read value

TIE_RESET[0] R/W 0 Hitless reference switch TIE reset.

1 = reset. This is a self clear bit.

Table 250: DPLL_CTRL_0 Register Index

Offset

(Hex)

Register Module Base Address: C600h

a

Individual Register Name Register Description

Loading...

Loading...