249©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

OUTPUT_0.OUT_DUTY_CYCLE_HIGH

Sets the output duty cycle high value

OUTPUT_0.OUT_CTRL_0

Configure output pad electrical characteristics.

Meet JEDEC compliance with LVDS operation by setting OUT_CTRL_0.PAD_VSWING = 0 and OUT_CTRL_0.PAD_VOS = 2.

Meet JEDEC compliance with 2.5 LVPECL operation by setting OUT_CTRL_0.PAD_VSWING = 2 and OUT_CTRL_0.PAD_VOS = 0.

Meet JEDEC compliance with 3.3 LVPECL operation by setting OUT_CTRL_0.PAD_VSWING = 2 and OUT_CTRL_0.PAD_VOS = 4.

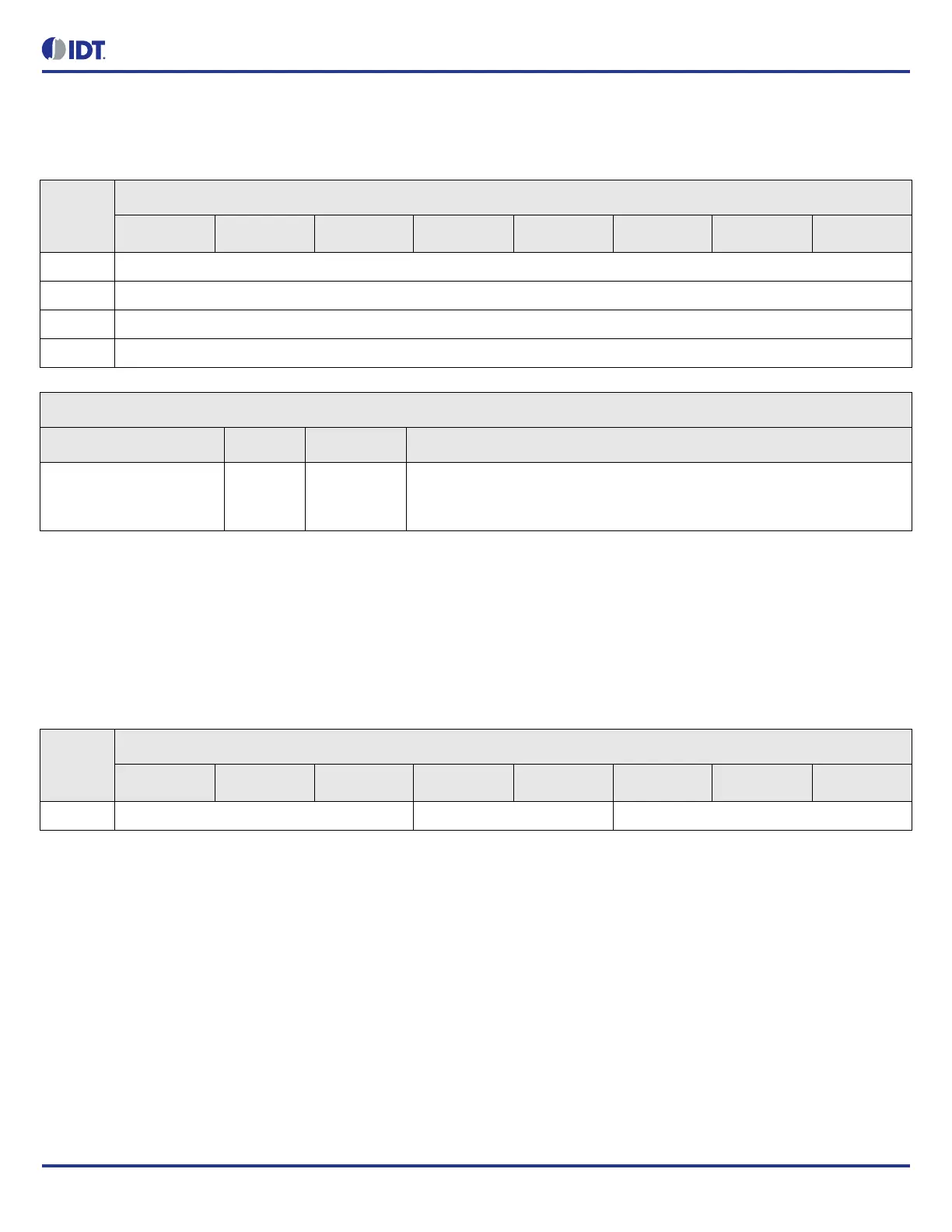

Table 325: OUTPUT_0.OUT_DUTY_CYCLE_HIGH Bit Field Locations and Descriptions

Offset

Address

(Hex)

OUTPUT_0.OUT_DUTY_CYCLE_HIGH Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

004h OUT_DUTY_CYCLE_HIGH[7:0]

005h OUT_DUTY_CYCLE_HIGH[15:8]

006h OUT_DUTY_CYCLE_HIGH[23:16]

007h OUT_DUTY_CYCLE_HIGH[31:24]

OUTPUT_0.OUT_DUTY_CYCLE_HIGH Bit Field Descriptions

Bit Field Name Field Type Default Value Description

OUT_DUTY_CYCLE_HIG

H[31:0]

R/W 0 Unsigned 32-bit divider high value.

The divider high value determines the high pulse width. The duty cycle is:

dc_high / (out_div - dc_high). If dc_high = 0, the duty cycle is 50 / 50.

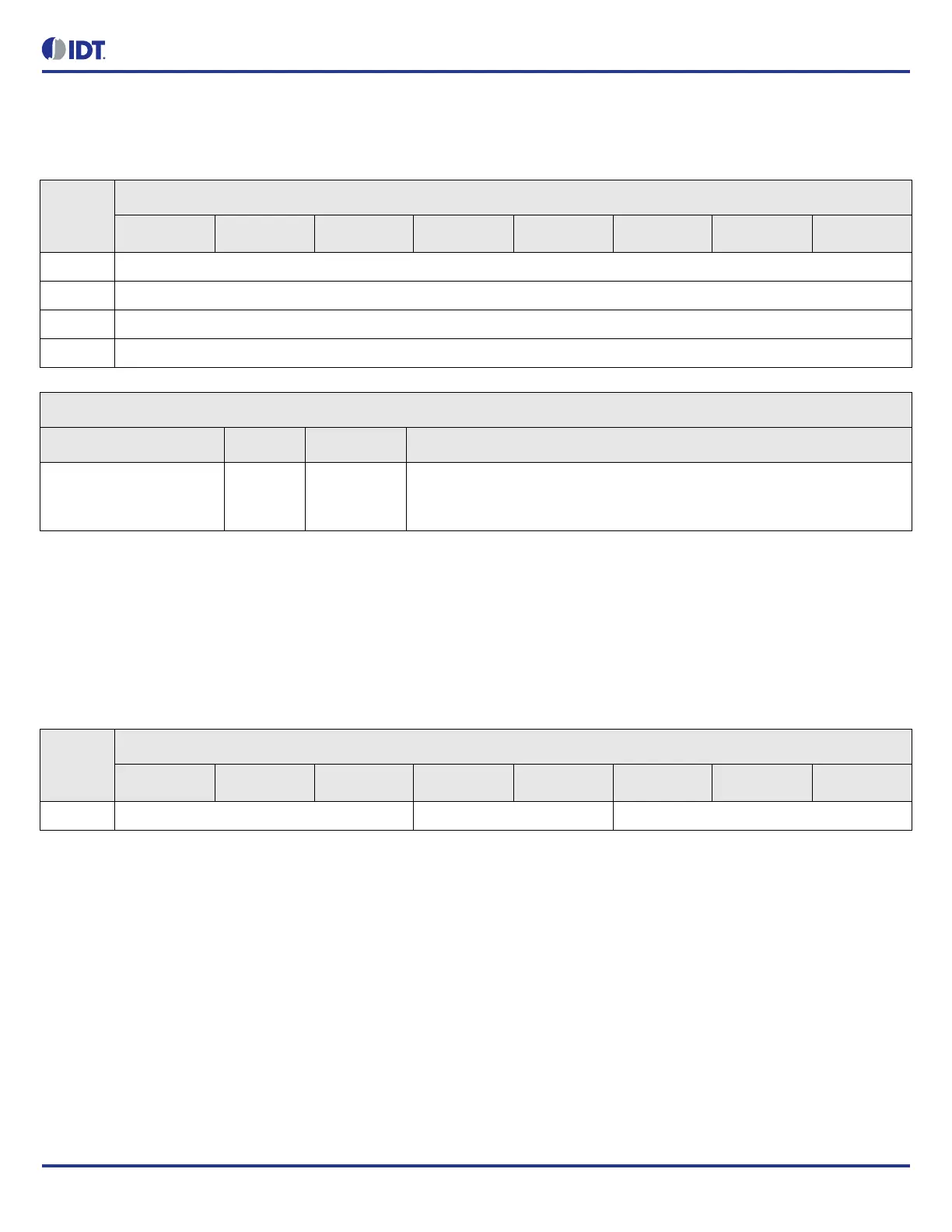

Table 326: OUTPUT_0.OUT_CTRL_0 Bit Field Locations and Descriptions

Offset

Address

(Hex)

OUTPUT_0.OUT_CTRL_0 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

008h PAD_VOS[7:5] PAD_VSWING[4:3] PAD_MODE[2:0]

Loading...

Loading...