34©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

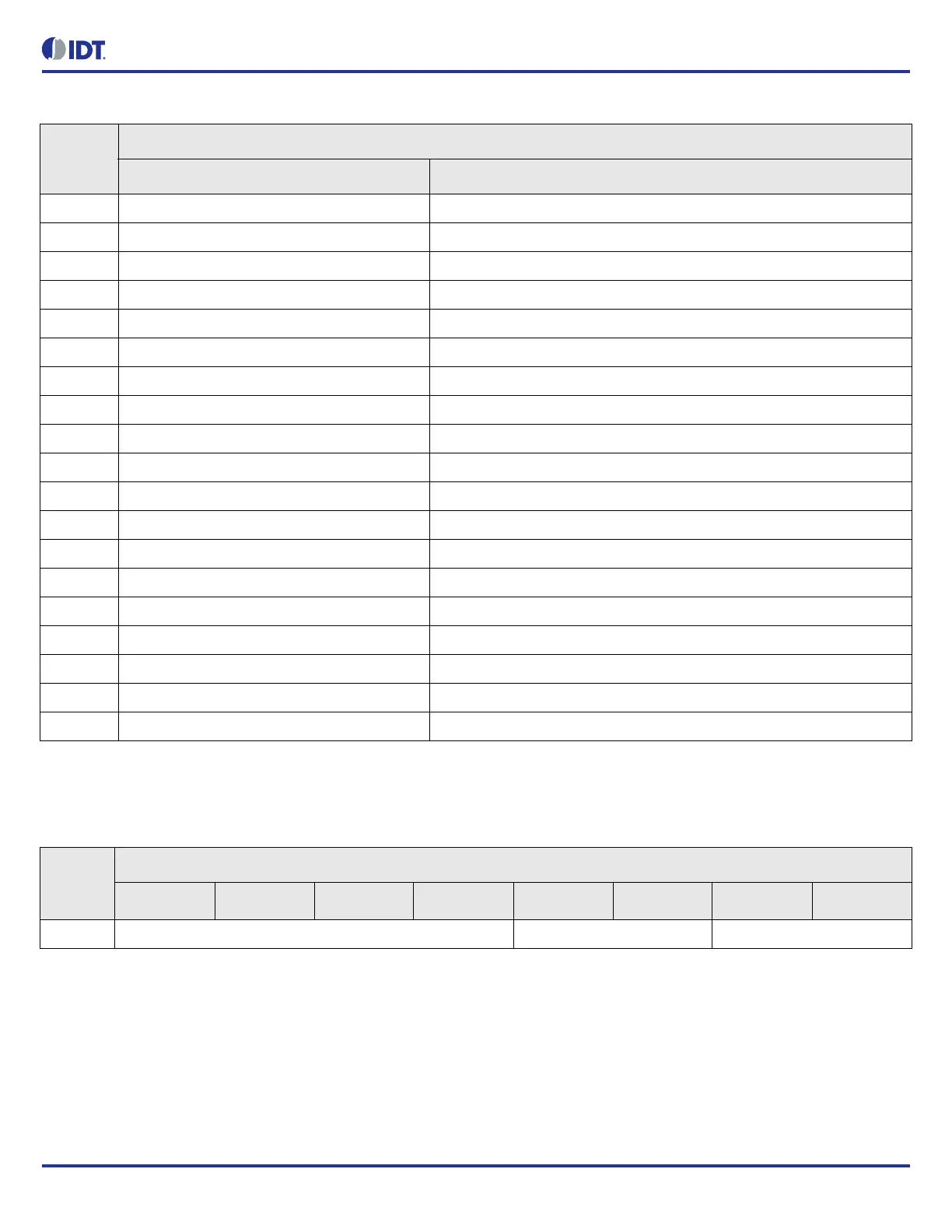

STATUS.I2CM_STATUS

Status of the I2C master (port selection and speed).

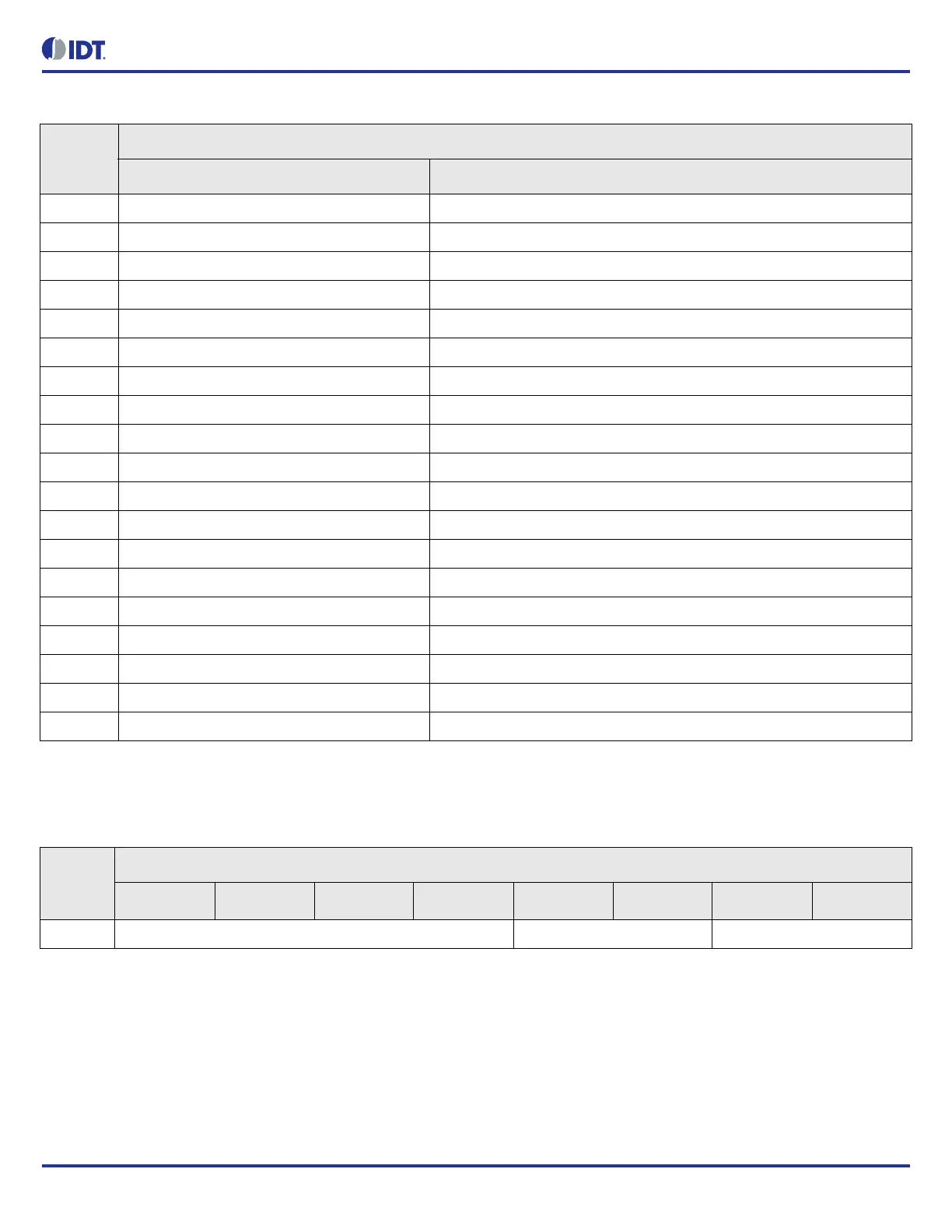

109h RESERVED This register must not be modified from the read value

10Ah RESERVED This register must not be modified from the read value

10Bh RESERVED This register must not be modified from the read value

10Ch STATUS.DPLL6_PHASE_STATUS Phase offset at output of decimator.

111h RESERVED This register must not be modified from the read value

112h RESERVED This register must not be modified from the read value

113h RESERVED This register must not be modified from the read value

114h STATUS.DPLL7_PHASE_STATUS Phase offset at output of decimator.

119h RESERVED This register must not be modified from the read value

11Ah RESERVED This register must not be modified from the read value

11Bh RESERVED This register must not be modified from the read value

11Ch STATUS.DPLL0_PHASE_PULL_IN_STATUS DPLL0 phase pull-in status

11Dh STATUS.DPLL1_PHASE_PULL_IN_STATUS DPLL1 phase pull-in status

11Eh STATUS.DPLL2_PHASE_PULL_IN_STATUS DPLL2 phase pull-in status

11Fh STATUS.DPLL3_PHASE_PULL_IN_STATUS DPLL3 phase pull-in status

120h STATUS.DPLL4_PHASE_PULL_IN_STATUS DPLL4 phase pull-in status

121h STATUS.DPLL5_PHASE_PULL_IN_STATUS DPLL5 phase pull-in status

122h STATUS.DPLL6_PHASE_PULL_IN_STATUS DPLL6 phase pull-in status

123h STATUS.DPLL7_PHASE_PULL_IN_STATUS DPLL7 phase pull-in status

Table 25: STATUS.I2CM_STATUS Bit Field Locations and Descriptions

Offset

Address

(Hex)

STATUS.I2CM_STATUS Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

000h RESERVED[7:4] I2CM_SPEED[3:2] I2CM_PORT_SEL[1:0]

Table 24: STATUS Register Index

Offset

(Hex)

Register Module Base Address: C03Ch

Individual Register Name Register Description

Loading...

Loading...