222©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

SYS_DPLL_CTRL.SYS_DPLL_PSL

System DPLL loop filter phase slope limit.

SYS_DPLL_CTRL.SYS_DPLL_PRED0_DAMPING

Predefined configuration 0 loop filter damping factor.

SYS_DPLL_CTRL.SYS_DPLL_BW Bit Field Descriptions

Bit Field Name Field Type Default Value Description

BW_UNIT[15:14] R/W 0 System DPLL loop filter bandwidth unit.

0 = uHz

1 = mHz

2 = Hz

3 = kHz

SYS_DPLL_BW[13:0] R/W 0 Unsigned 14-bit system DPLL loop filter bandwidth value.

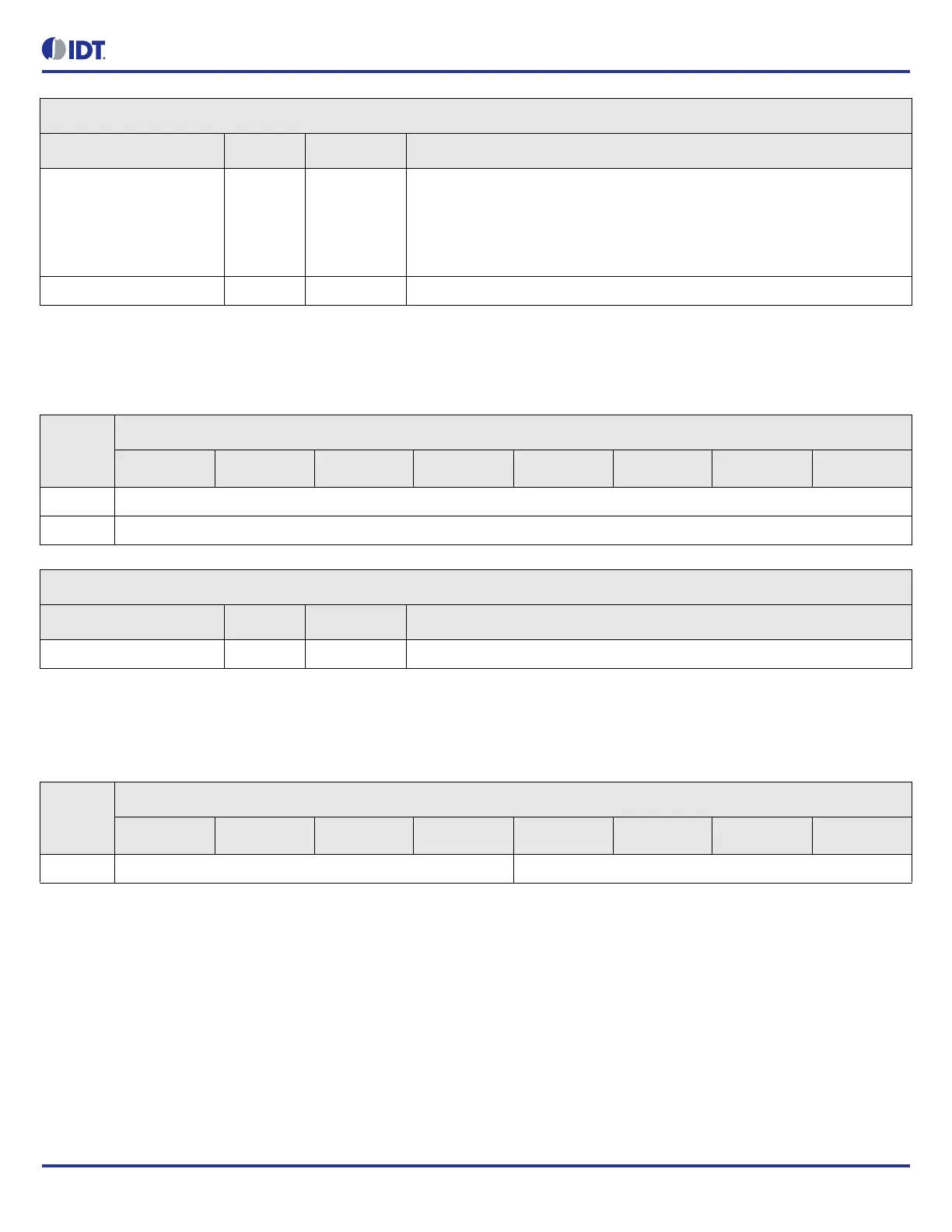

Table 281: SYS_DPLL_CTRL.SYS_DPLL_PSL Bit Field Locations and Descriptions

Offset

Address

(Hex)

SYS_DPLL_CTRL.SYS_DPLL_PSL Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

006h SYS_DPLL_PSL[7:0]

007h SYS_DPLL_PSL[15:8]

SYS_DPLL_CTRL.SYS_DPLL_PSL Bit Field Descriptions

Bit Field Name Field Type Default Value Description

SYS_DPLL_PSL[15:0] R/W 0 Unsigned 16-bit loop filter phase slope limit in ns/s.

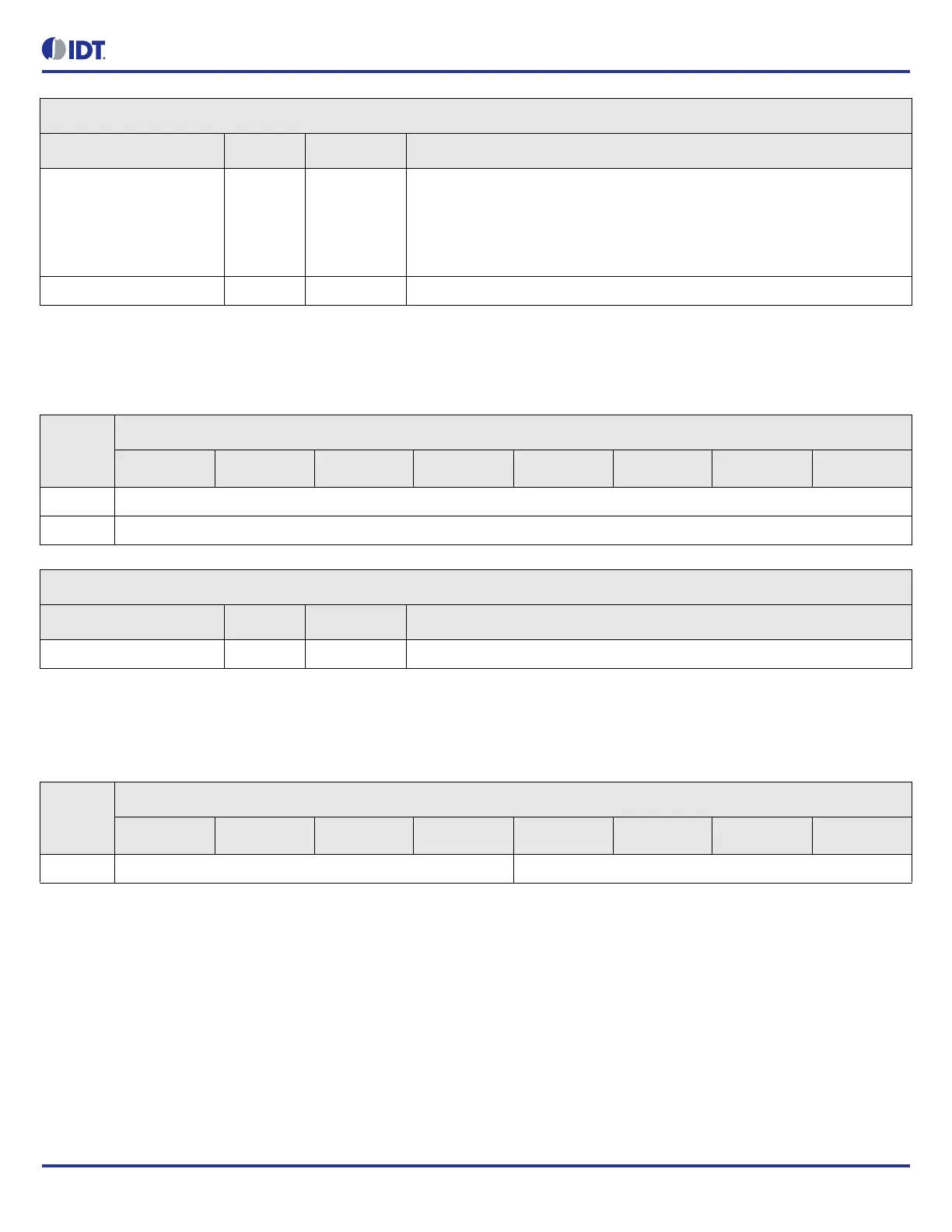

Table 282: SYS_DPLL_CTRL.SYS_DPLL_PRED0_DAMPING Bit Field Locations and Descriptions

Offset

Address

(Hex)

SYS_DPLL_CTRL.SYS_DPLL_PRED0_DAMPING Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

008h RESERVED[7:4] DAMP_FTR[3:0]

Loading...

Loading...