70©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

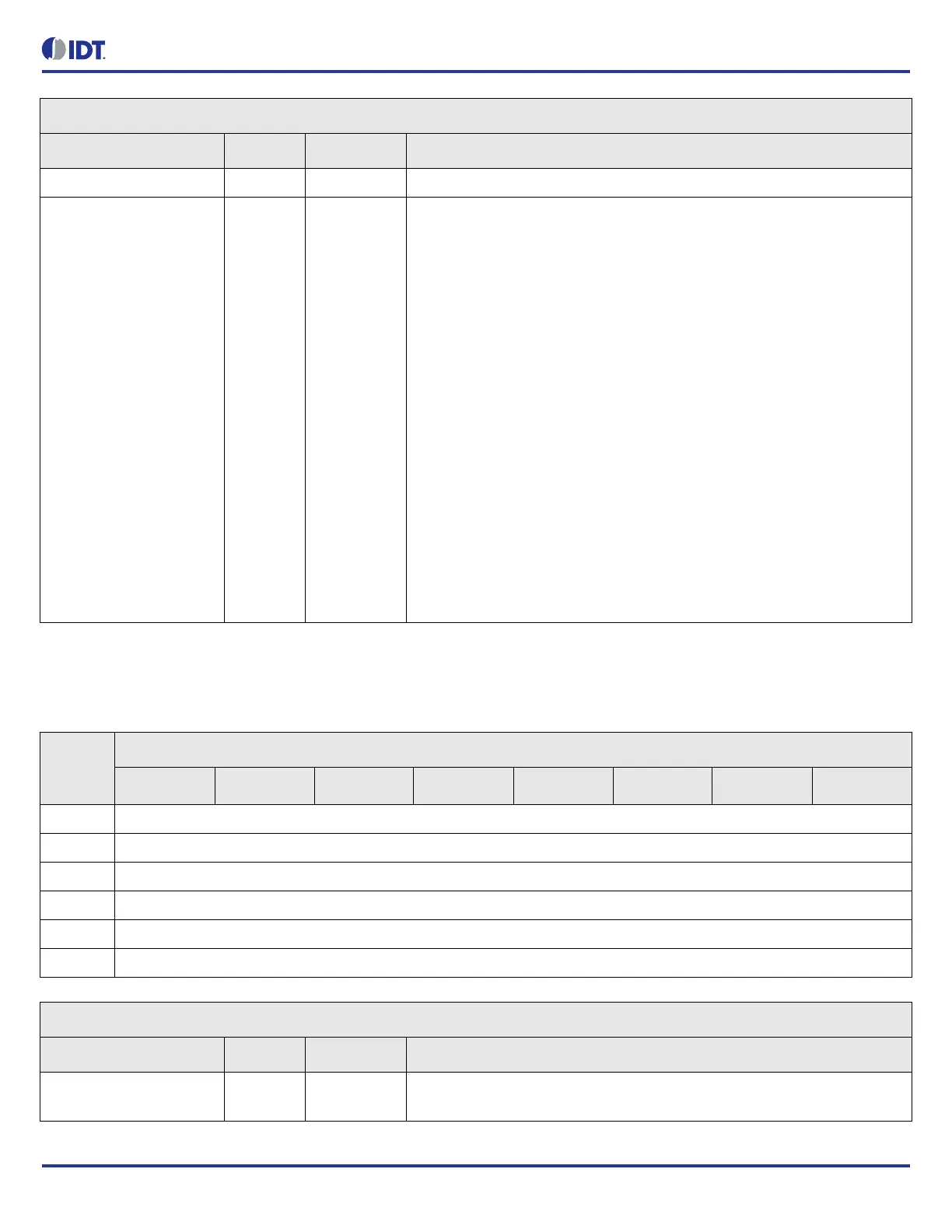

STATUS.DPLL0_FILTER_STATUS

DPLL 0 loop filter status.

STATUS.DPLL_SYS_REF_STAT Bit Field Descriptions

Bit Field Name Field Type Default Value Description

RESERVED N/A - This field must not be modified from the read value

DPLL_SYS_INPUT[4:0] R/O 0 Current reference input for system DPLL.

0x00 = CLK0

0x01 = CLK1

0x02 = CLK2

0x03 = CLK3

0x04 = CLK4

0x05 = CLK5

0x06 = CLK6

0x07 = CLK7

0x08 = CLK8

0x09 = CLK9

0x0A = CLK10

0x0B = CLK11

0x0C = CLK12

0x0D = CLK13

0x0E = CLK14

0x0F = CLK15

0x10 = write-phase input

0x11 = write-frequency input

0x12 = XO_DPLL

0x1F = no reference

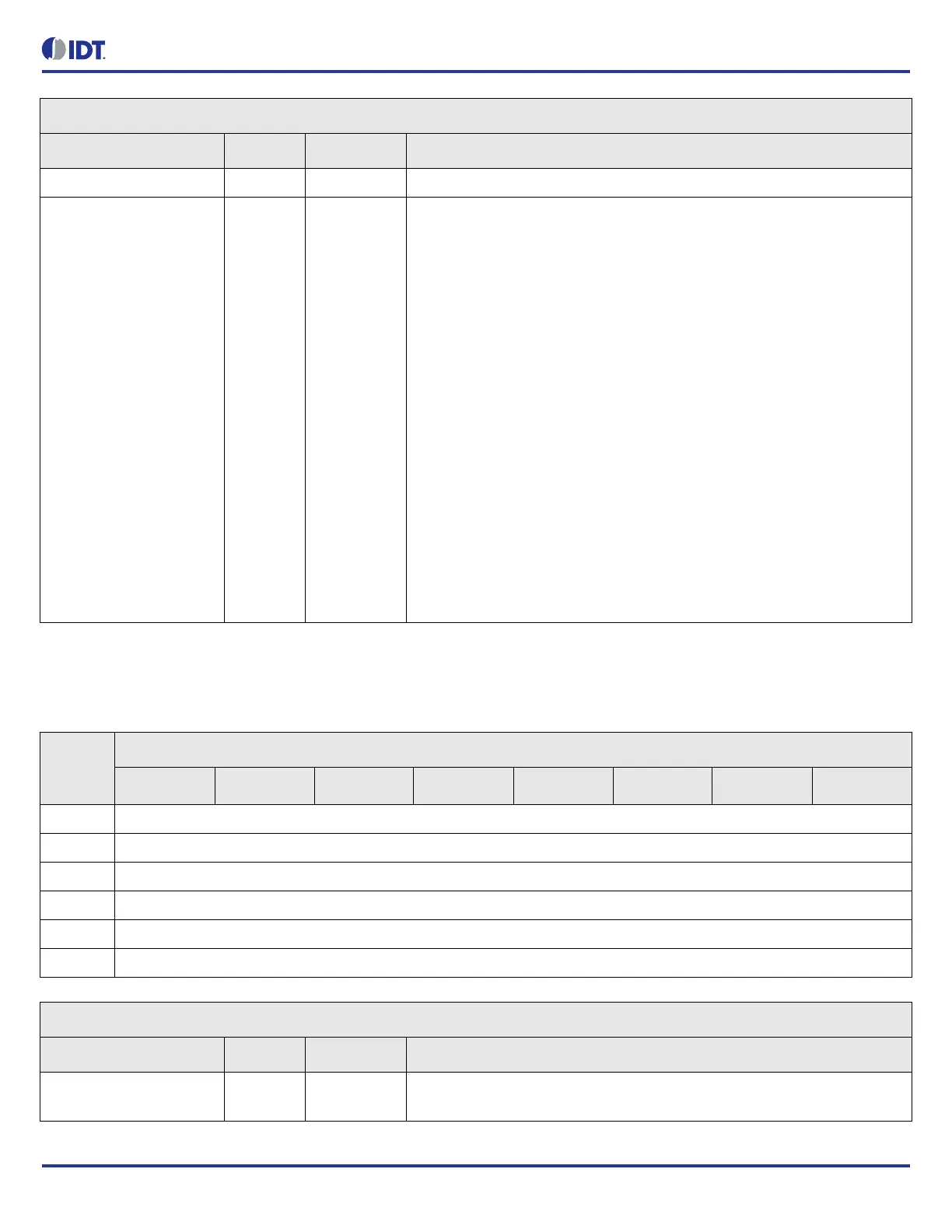

Table 67: STATUS.DPLL0_FILTER_STATUS Bit Field Locations and Descriptions

Offset

Address

(Hex)

STATUS.DPLL0_FILTER_STATUS Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

044h FILTER_STATUS[7:0]

045h FILTER_STATUS[15:8]

046h FILTER_STATUS[23:16]

047h FILTER_STATUS[31:24]

048h FILTER_STATUS[39:32]

049h FILTER_STATUS[47:40]

STATUS.DPLL0_FILTER_STATUS Bit Field Descriptions

Bit Field Name Field Type Default Value Description

FILTER_STATUS[47:0] R/O 0 DPLL loop filter status.

Fine phase measurement in units of 50/128 picoseconds.

Loading...

Loading...