149©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

DPLL_0.DPLL_LOCK_2

Frequency lock threshold.

DPLL_0.DPLL_LOCK_3

The duration in seconds the frequency has to be locked before declaring locked.

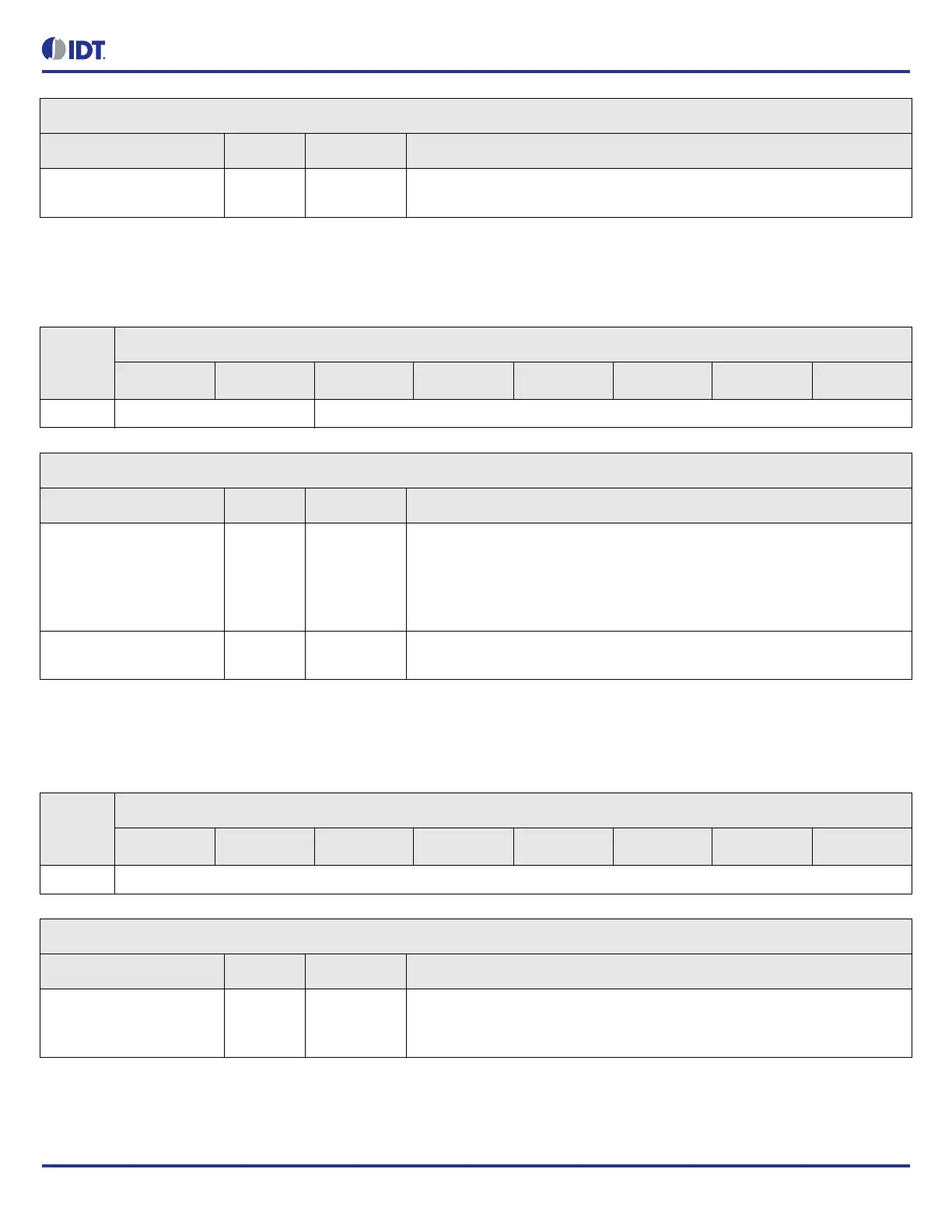

DPLL_0.DPLL_LOCK_1 Bit Field Descriptions

Bit Field Name Field Type Default Value Description

PHASE_MON_DUR[7:0] R/W 0 Duration of phase error monitoring before lock is declared, in seconds.

0 means 4000 microseconds.

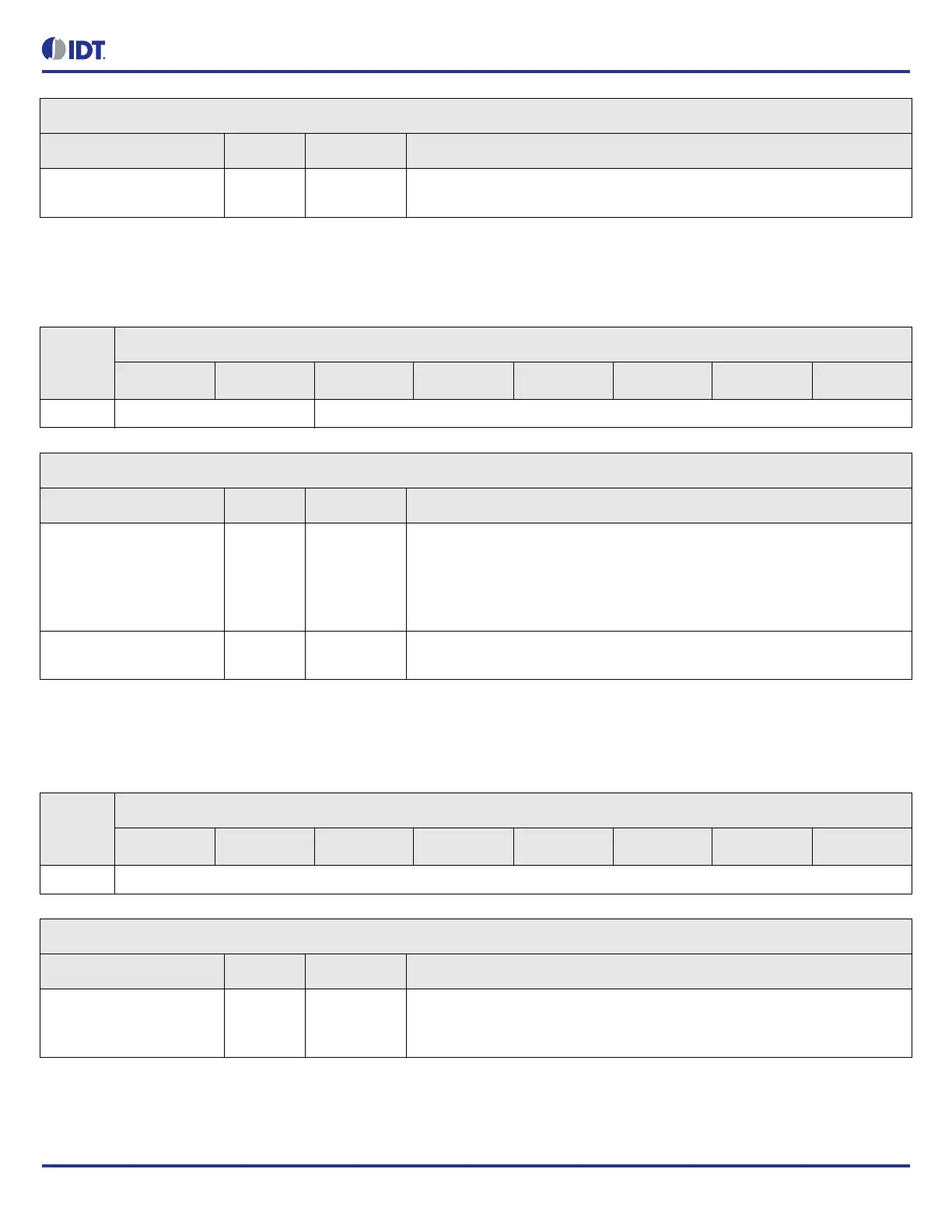

Table 184: DPLL_0.DPLL_LOCK_2 Bit Field Locations and Descriptions

Offset

Address

(Hex)

DPLL_0.DPLL_LOCK_2 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

00Dh FFO_UNIT[7:6] FFO_LOCK_MAX_ERROR[5:0]

DPLL_0.DPLL_LOCK_2 Bit Field Descriptions

Bit Field Name Field Type Default Value Description

FFO_UNIT[7:6] R/W 0 FFO error unit.

0 = 1 ppb

1 = 10 ppb

2 = 100 ppb

3 = 1 ppm

FFO_LOCK_MAX_ERROR

[5:0]

R/W 0 Integer maximum FFO error for lock criteria.

If 0, then Fractional Frequency Offset check is disabled.

Table 185: DPLL_0.DPLL_LOCK_3 Bit Field Locations and Descriptions

Offset

Address

(Hex)

DPLL_0.DPLL_LOCK_3 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

00Eh FFO_MON_DUR[7:0]

DPLL_0.DPLL_LOCK_3 Bit Field Descriptions

Bit Field Name Field Type Default Value Description

FFO_MON_DUR[7:0] R/W 0 Duration of FFO error monitoring before lock declared (seconds).

0 means that the frequency is declared locked immediately after FFO lock

criteria is met.

Loading...

Loading...