147©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

DPLL_0.DPLL_HO_ADVCD_BW

DPLL advanced holdover bandwidth configuration.

DPLL_0.DPLL_HO_CFG

Select type of holdover to be used.

DPLL_0.DPLL_HO_ADVCD_HISTORY Bit Field Descriptions

Bit Field Name Field Type Default Value Description

RESERVED N/A - This field must not be modified from the read value

HISTORY[5:0] R/W 0 Configure DPLL holdover history.

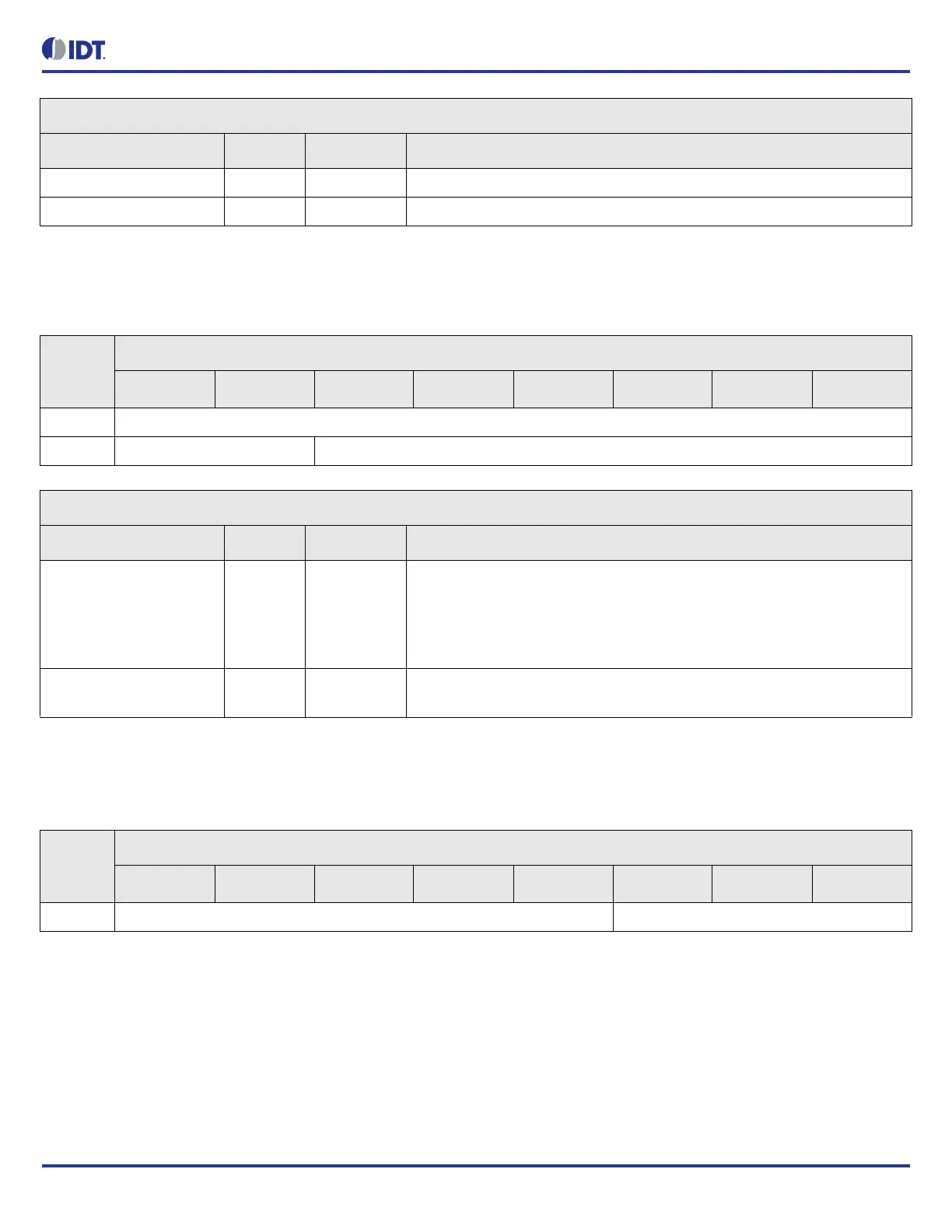

Table 180: DPLL_0.DPLL_HO_ADVCD_BW Bit Field Locations and Descriptions

Offset

Address

(Hex)

DPLL_0.DPLL_HO_ADVCD_BW Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

008h DPLL_HO_ADVCD_BW[7:0]

009h BW_UNIT[15:14] DPLL_HO_ADVCD_BW[13:8]

DPLL_0.DPLL_HO_ADVCD_BW Bit Field Descriptions

Bit Field Name Field Type Default Value Description

BW_UNIT[15:14] R/W 0 DPLL advanced holdover bandwidth unit.

0 = uHz

1 = mHz

2 = Hz

3 = kHz

DPLL_HO_ADVCD_BW[13

:0]

R/W 0 Unsigned 14 bit DPLL advanced holdover bandwidth value.

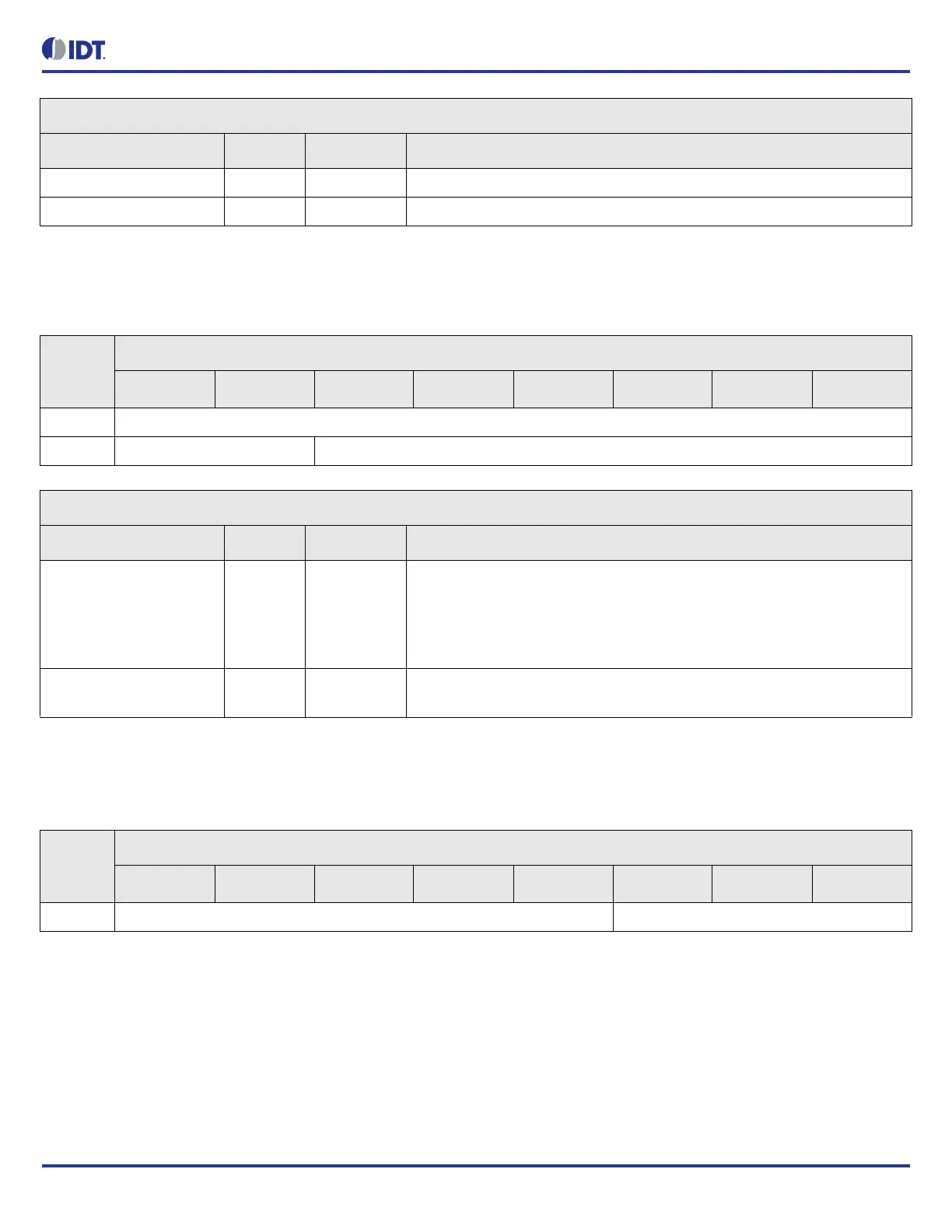

Table 181: DPLL_0.DPLL_HO_CFG Bit Field Locations and Descriptions

Offset

Address

(Hex)

DPLL_0.DPLL_HO_CFG Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

00Ah RESERVED[7:3] HOLDOVER_MODE[2:0]

Loading...

Loading...