233©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

GPIO_0.GPIO_DCO_INC_DEC

Increment/decrement DCO FFO configuration. Applies when GPIO_FUNCTION is equal to 'inc DCO FFO' or 'dec DCO FFO'. The squelch

level is determined by the configuration per output by OUTPUT_n.OUT_CTR_1.SQUELCH_VALUE.

GPIO_0.GPIO_OUT_CTRL_0

Define the set of outputs to be squelched by this GPIO input. Applies when GPIO_FUNCTION is equal to 'clock output control'. The squelch

level is determined by OUTPUT_n.OUT_CTRL_1.SQUELCH_VALUE.

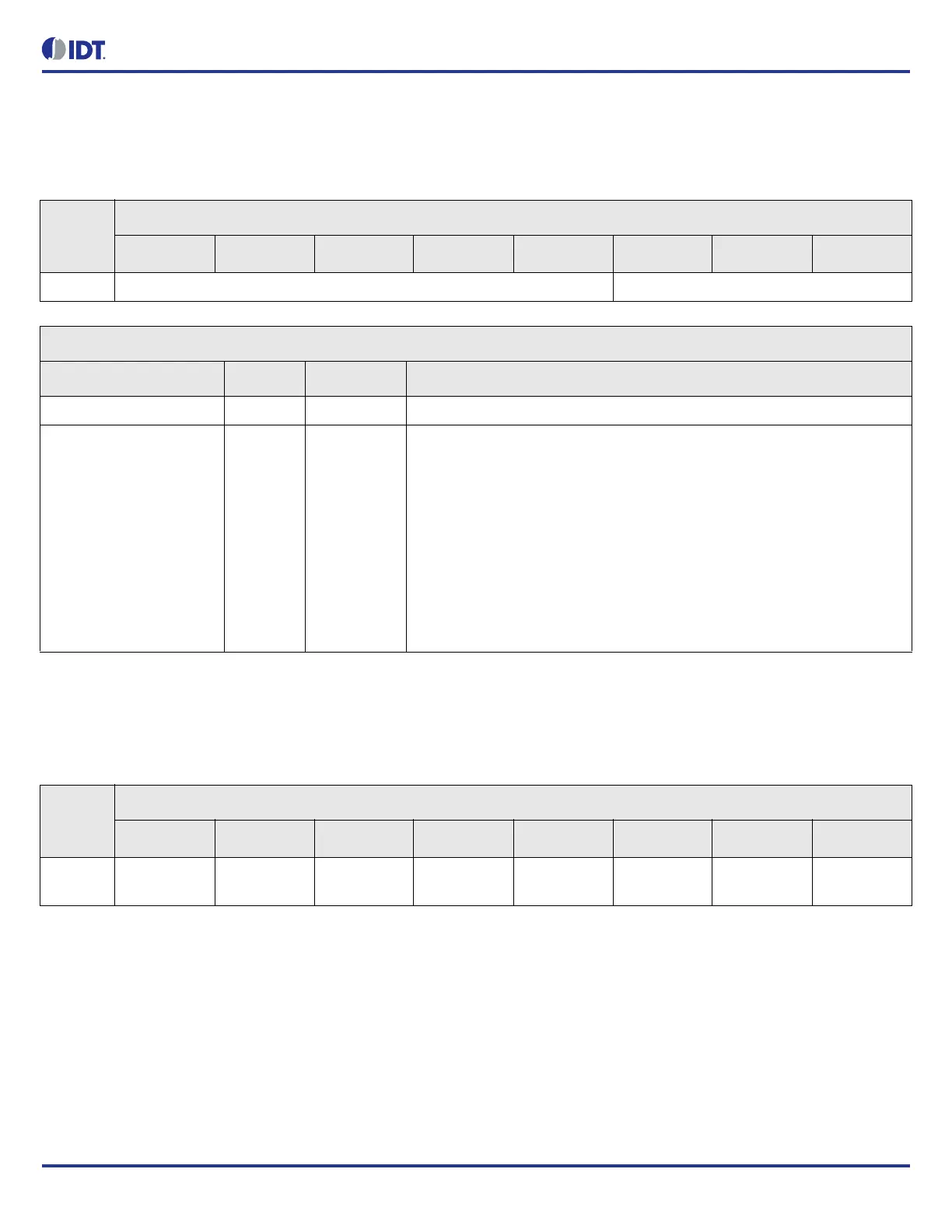

Table 303: GPIO_0.GPIO_DCO_INC_DEC Bit Field Locations and Descriptions

Offset

Address

(Hex)

GPIO_0.GPIO_DCO_INC_DEC Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

000h RESERVED[7:3] DPLL_INDEX[2:0]

GPIO_0.GPIO_DCO_INC_DEC Bit Field Descriptions

Bit Field Name Field Type Default Value Description

RESERVED N/A - This field must not be modified from the read value

DPLL_INDEX[2:0] R/W 0 DPLL index.

Select the DPLL to be controlled by this GPIO in incremental/decremental

mode.

0 = DPLL0

1 = DPLL1

2 = DPLL2

3 = DPLL3

4 = DPLL4

5 = DPLL5

6 = DPLL6

7 = DPLL7

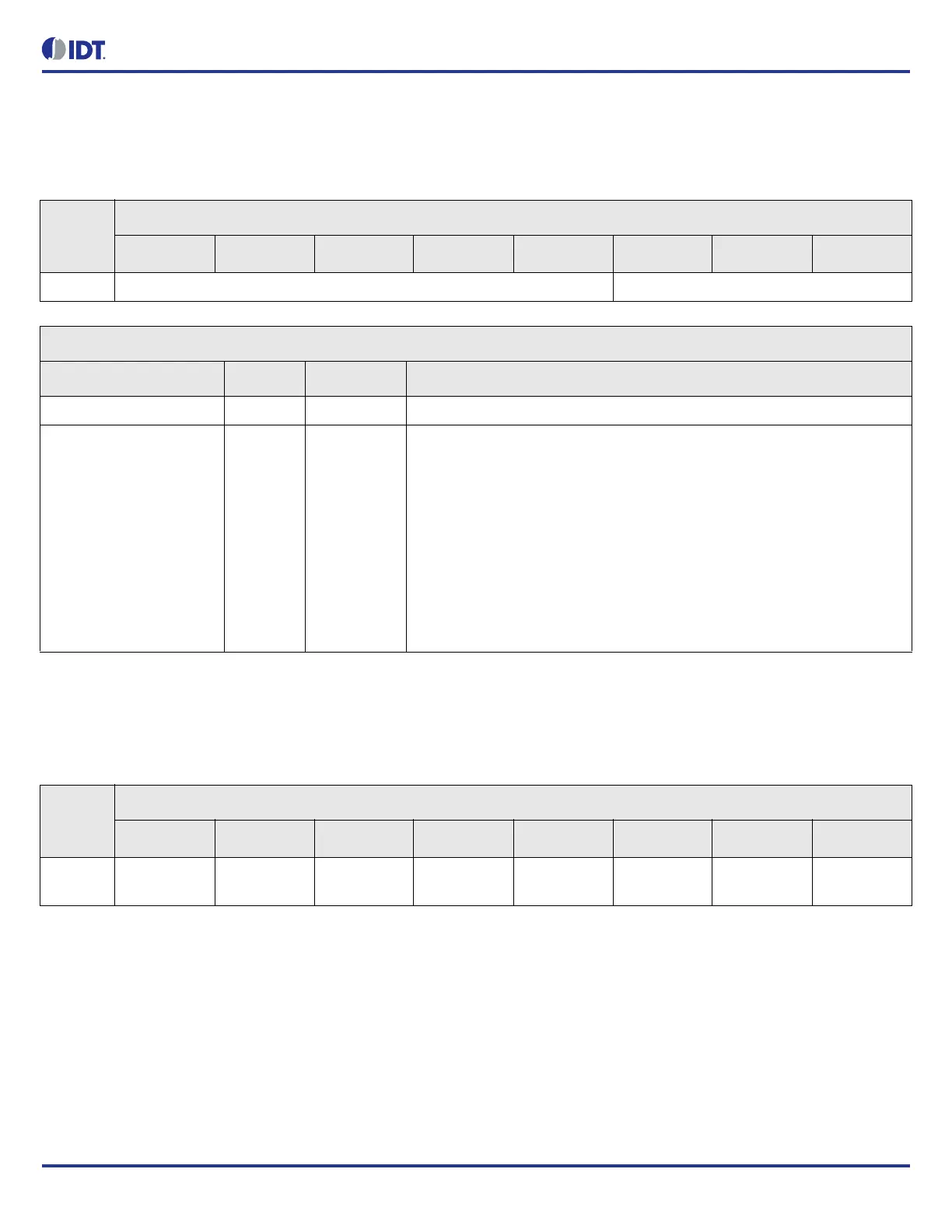

Table 304: GPIO_0.GPIO_OUT_CTRL_0 Bit Field Locations and Descriptions

Offset

Address

(Hex)

GPIO_0.GPIO_OUT_CTRL_0 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

001h CTRL_OUT_

7[7]

CTRL_OUT_

6[6]

CTRL_OUT_

5[5]

CTRL_OUT_

4[4]

CTRL_OUT_

3[3]

CTRL_OUT_

2[2]

CTRL_OUT_

1[1]

CTRL_OUT_

0[0]

Loading...

Loading...