183©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

SYS_DPLL.SYS_DPLL_LOCK_1

Phase lock monitor duration.

SYS_DPLL.SYS_DPLL_LOCK_2

Frequency lock threshold.

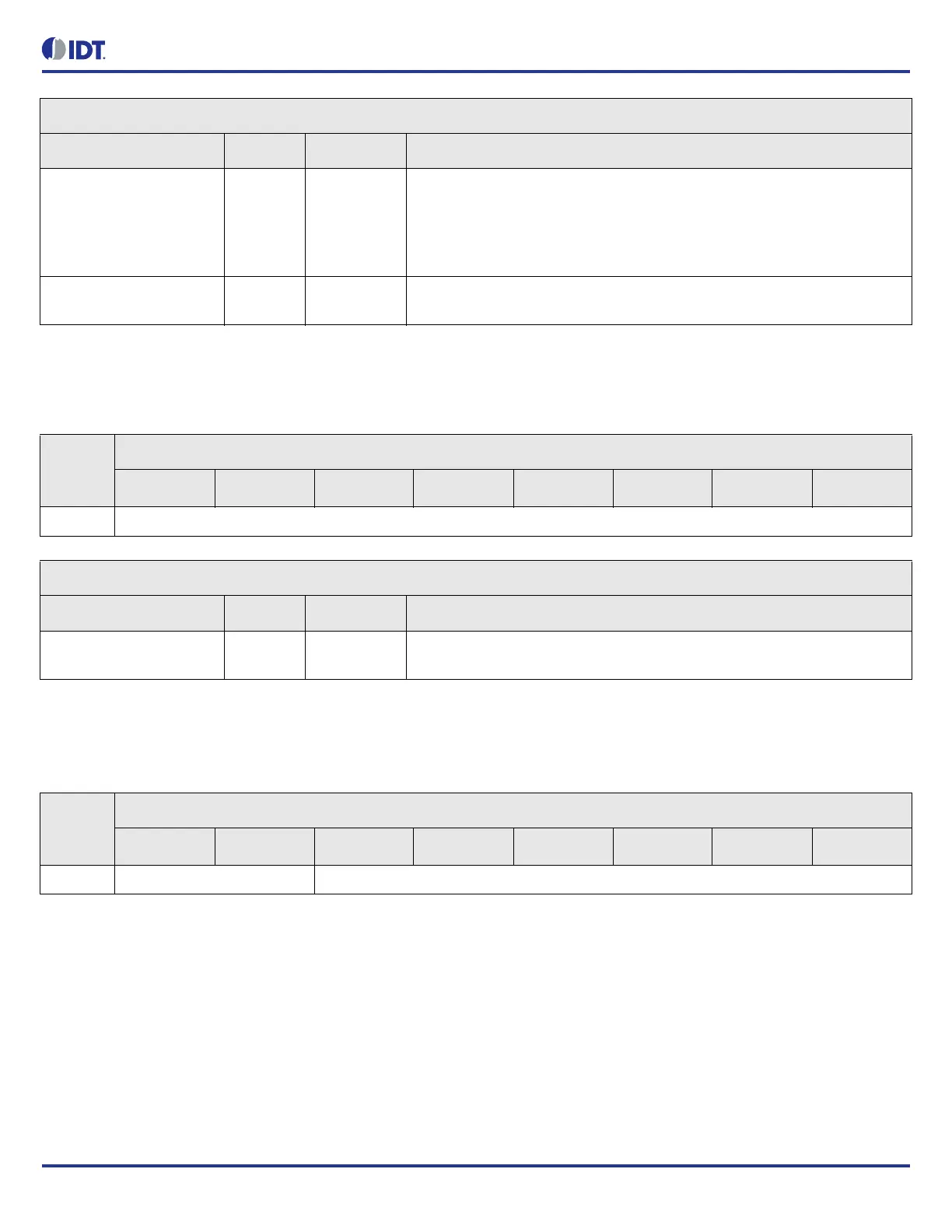

SYS_DPLL.SYS_DPLL_LOCK_0 Bit Field Descriptions

Bit Field Name Field Type Default Value Description

PHASE_UNIT[7:6] R/W 0 Phase lock threshold unit.

0 = 1 ns

1 = 10 ns

2 = 100 ns

3 = 1 us

PHASE_LOCK_MAX_ERR

OR[5:0]

R/W 0 Phase lock threshold value.

If 0, then Fractional Frequency Offset check is disabled.

Table 226: SYS_DPLL.SYS_DPLL_LOCK_1 Bit Field Locations and Descriptions

Offset

Address

(Hex)

SYS_DPLL.SYS_DPLL_LOCK_1 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

004h PHASE_MON_DUR[7:0]

SYS_DPLL.SYS_DPLL_LOCK_1 Bit Field Descriptions

Bit Field Name Field Type Default Value Description

PHASE_MON_DUR[7:0] R/W 0 Duration of phase error monitoring before lock is declared, in seconds.

0 means 4000 microseconds.

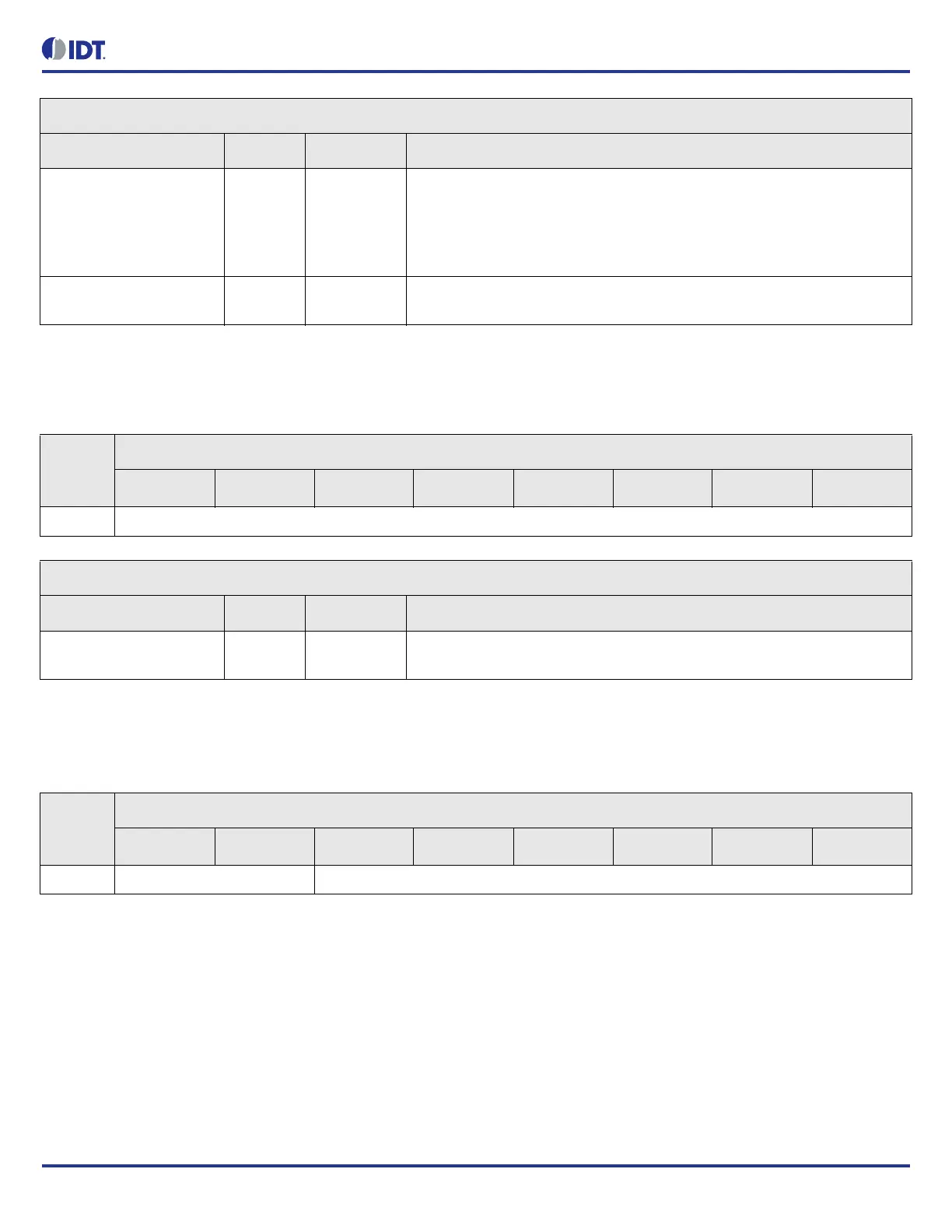

Table 227: SYS_DPLL.SYS_DPLL_LOCK_2 Bit Field Locations and Descriptions

Offset

Address

(Hex)

SYS_DPLL.SYS_DPLL_LOCK_2 Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

005h FFO_UNIT[7:6] FFO_LOCK_MAX_ERROR[5:0]

Loading...

Loading...