141©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

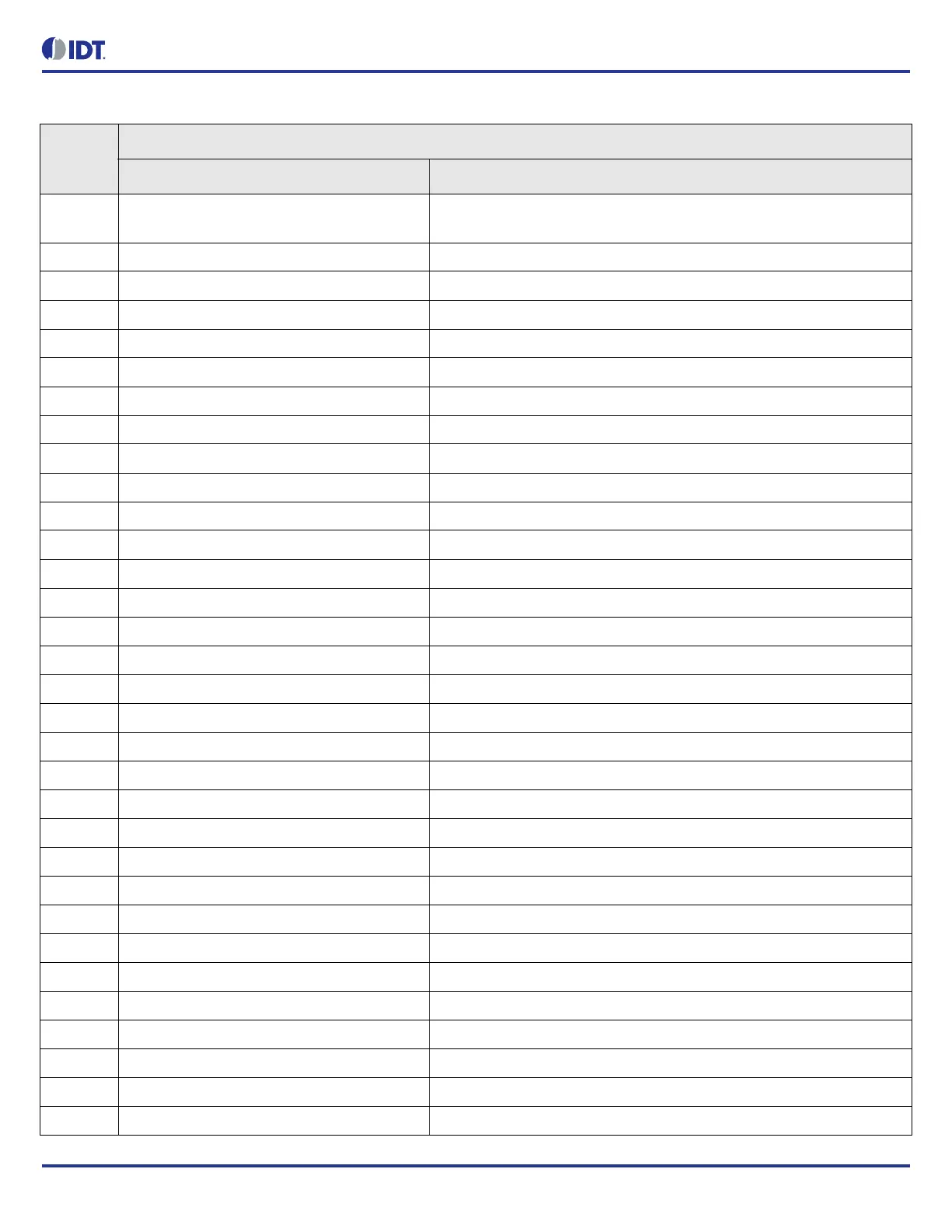

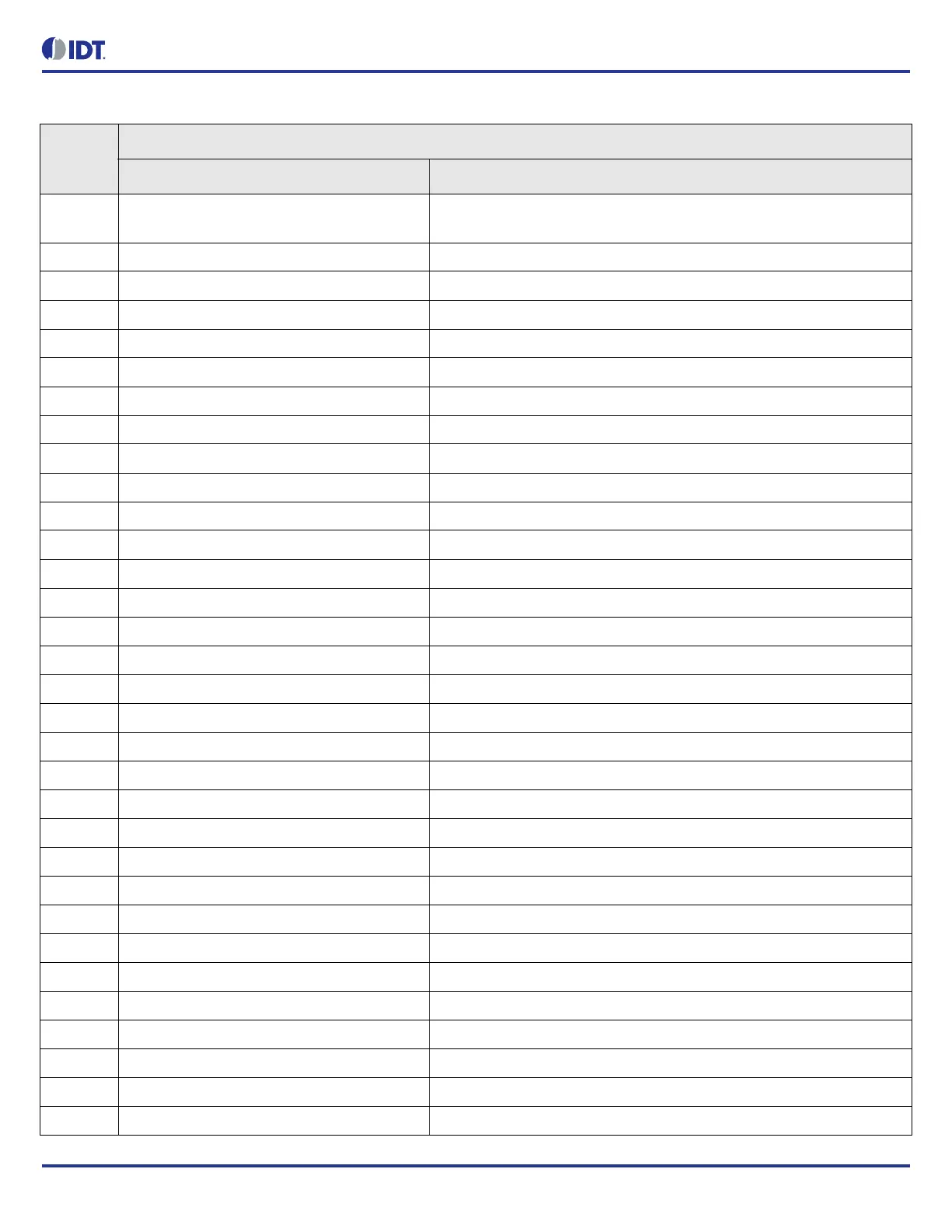

006h DPLL_0.DPLL_FILTER_STATUS_UPDATE_CF

G

DPLL loop filter status update configuration.

007h DPLL_0.DPLL_HO_ADVCD_HISTORY Advanced holdover history configuration.

008h DPLL_0.DPLL_HO_ADVCD_BW DPLL advanced holdover bandwidth configuration.

00Ah DPLL_0.DPLL_HO_CFG Holdover configuration.

00Bh DPLL_0.DPLL_LOCK_0 Phase lock threshold.

00Ch DPLL_0.DPLL_LOCK_1 Phase lock monitor duration.

00Dh DPLL_0.DPLL_LOCK_2 Frequency lock threshold.

00Eh DPLL_0.DPLL_LOCK_3 Frequency lock monitor duration.

00Fh DPLL_0.DPLL_REF_PRIORITY_0 Select input for highest (0) priority.

010h DPLL_0.DPLL_REF_PRIORITY_1 Select input for priority 1.

011h DPLL_0.DPLL_REF_PRIORITY_2 Select input for priority 2.

012h DPLL_0.DPLL_REF_PRIORITY_3 Select input for priority 3.

013h DPLL_0.DPLL_REF_PRIORITY_4 Select input for priority 4.

014h DPLL_0.DPLL_REF_PRIORITY_5 Select input for priority 5.

015h DPLL_0.DPLL_REF_PRIORITY_6 Select input for priority 6.

016h DPLL_0.DPLL_REF_PRIORITY_7 Select input for priority 7.

017h DPLL_0.DPLL_REF_PRIORITY_8 Select input for priority 8.

018h DPLL_0.DPLL_REF_PRIORITY_9 Select input for priority 9.

019h DPLL_0.DPLL_REF_PRIORITY_10 Select input for priority 10.

01Ah DPLL_0.DPLL_REF_PRIORITY_11 Select input for priority 11.

01Bh DPLL_0.DPLL_REF_PRIORITY_12 Select input for priority 12.

01Ch DPLL_0.DPLL_REF_PRIORITY_13 Select input for priority 13.

01Dh DPLL_0.DPLL_REF_PRIORITY_14 Select input for priority 14.

01Eh DPLL_0.DPLL_REF_PRIORITY_15 Select input for priority 15.

01Fh DPLL_0.DPLL_REF_PRIORITY_16 Select input for priority 16.

020h DPLL_0.DPLL_REF_PRIORITY_17 Select input for priority 17.

021h DPLL_0.DPLL_REF_PRIORITY_18 Select input for priority 18.

022h RESERVED This register must not be modified from the read value

023h DPLL_0.DPLL_FASTLOCK_CFG_0 Fast lock configuration.

024h DPLL_0.DPLL_FASTLOCK_CFG_1 Fast lock configuration.

025h DPLL_0.DPLL_MAX_FREQ_OFFSET DPLL maximum frequency offset limit.

026h DPLL_0.DPLL_FASTLOCK_PSL Fast lock phase slope limit.

Table 172: DPLL_0 Register Index

Offset

(Hex)

Register Module Base Address: C3B0h

a

Individual Register Name Register Description

Loading...

Loading...