5©2018 Integrated Device Technology, Inc September 12, 2018

8A3xxxx Family Programming Guide

I

2

C burst mode operation is required to ensure data integrity of multi-byte registers. When accessing a multi-byte register, all data bytes must

be written or read in a single I

2

C burst access. Bursts may be of greater length if desired, but must not extend beyond the end of the register

page (Offset Addr FFh in 1B mode, no limit in 2B mode). An internal address pointer is incremented automatically as each data byte is written

or read.

2

C 1-byte (1B) Addressing Examples

8A3xxxx I

2

C 7-bit I

2

C address is 0x5B with LSB=R/W

Example Write “0x50” to register 0xCBE4

B6* FC 00 CB 10 20 #Set Page Register, *I

2

C Address is left-shifted one bit.

B6 E4 50 #Write data 5B to CB E4

I

2

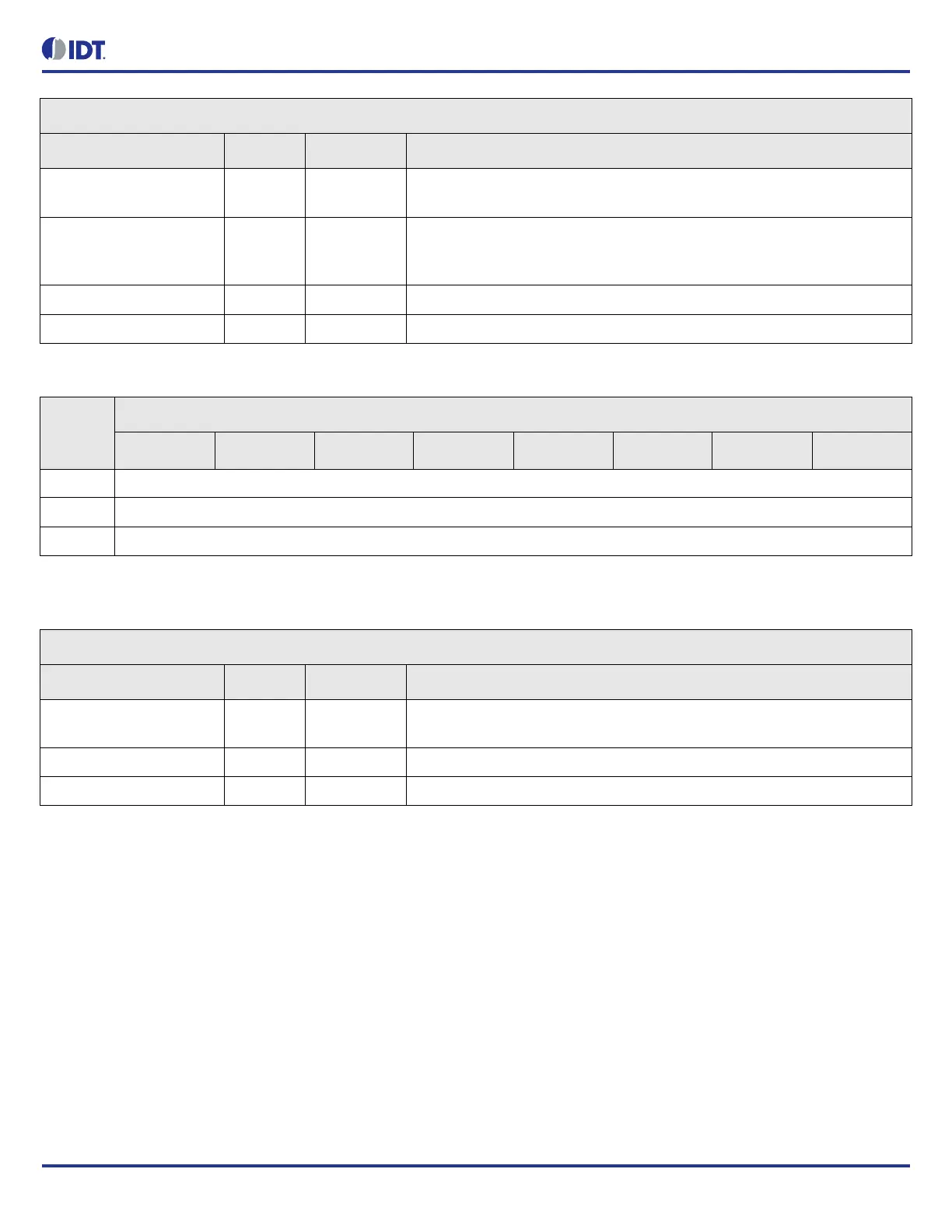

C 1B Mode Page Register Bit Field Descriptions

Bit Field Name Field Type Default Value Description

PAGE_ADDR[7:0] R/W 00h The values in this field are always replaced by the bits in I

2

C transaction itself

and so have no meaning.

PAGE_ADDR[15:8] R/W 00h Select which register page to access. Forms the upper 8-bits of the 16-bit

register address. Only values of 80h or higher should be used. Lower addresses

are not user-accessible

PAGE_ADDR[23:16] R/W 10h Must be set to 10h in all cases

PAGE_ADDR[31:24] R/W 20h Must be set to 20h in all cases

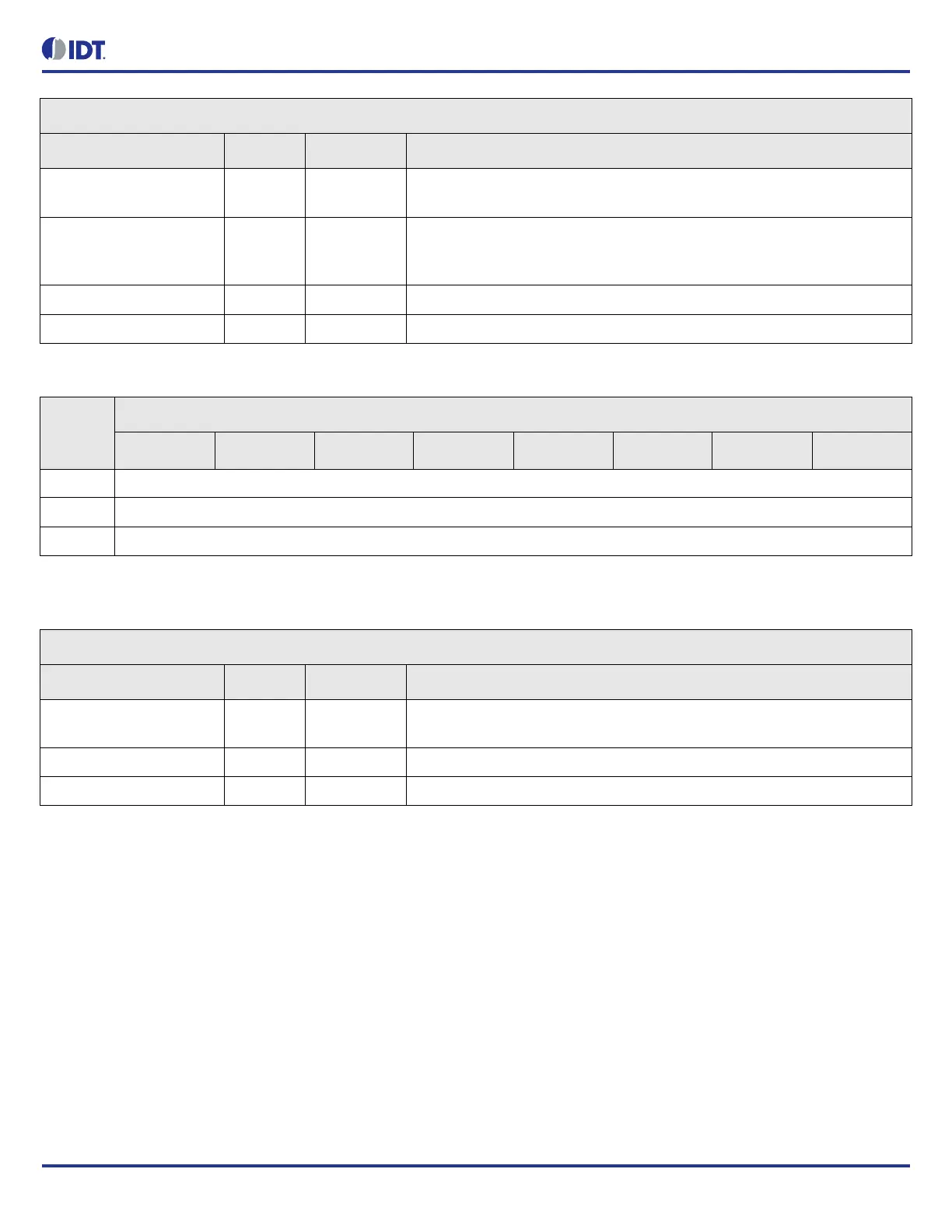

Table 3: I

2

C 2B Mode Page Register Bit Field Locations and Descriptions

Offset

Address

(Hex)

I

2

C 2B Mode Page Register Bit Field Locations

D7 D6 D5 D4 D3 D2 D1 D0

FFFD

1

PAGE_ADDR[15:8]

FFFE PAGE_ADDR[23:16]

FFFF PAGE_ADDR[31:24]

1. Burst access must begin at this non-aligned offset and all 3 bytes must be written in the same I

2

C burst access. A burst beginning at the

32-bit aligned address of FFFCh will not correctly set this register.

I

2

C 2B Mode Page Register Bit Field Descriptions

Bit Field Name Field Type Default Value Description

PAGE_ADDR[15:8] R/W 00h The values in this field are always replaced by the bits in I

2

C transaction itself

and so have no meaning.

PAGE_ADDR[23:16] R/W 10h Must be set to 10h in all cases

PAGE_ADDR[31:24] R/W 20h Must be set to 20h in all cases

Loading...

Loading...