2-62 Computer Group Literature Center Web Site

Raven PCI Host Bridge & Multi-Processor Interrupt Controller

2

R RESET CONTROLLER. Writing a one to this bit forces the

controller logic to be reset. This bit is cleared automatically when the reset

sequence is complete. While this bit is set, the values of all other register

are undefined.

M CASCADE MODE. Allows cascading of an external 8259 pair

connected to the first interrupt source input pin (0). In the pass through

mode, interrupt source 0 is passed directly through to the processor 0 INT

pin. Raven MPIC is essentially disabled. In the mixed mode, 8259

interrupts are delivered using the priority and distribution mechanism of

Raven MPIC. The Vector/Priority and Destination registers for interrupt

source 0 are used to control the delivery mode for all 8259 generated

interrupt sources.

T Tie Mode. Writing a one to this register bit will cause a tie in external

interrupt processing to, swap back and forth between processor 0 and 1.

The first tie in external interrupt processing always goes to Processor 0

after a reset. When this register bit is set to 0, a tie in external interrupt

processing will always go to processor 0 (Mode used on Version $02 of

MPIC).

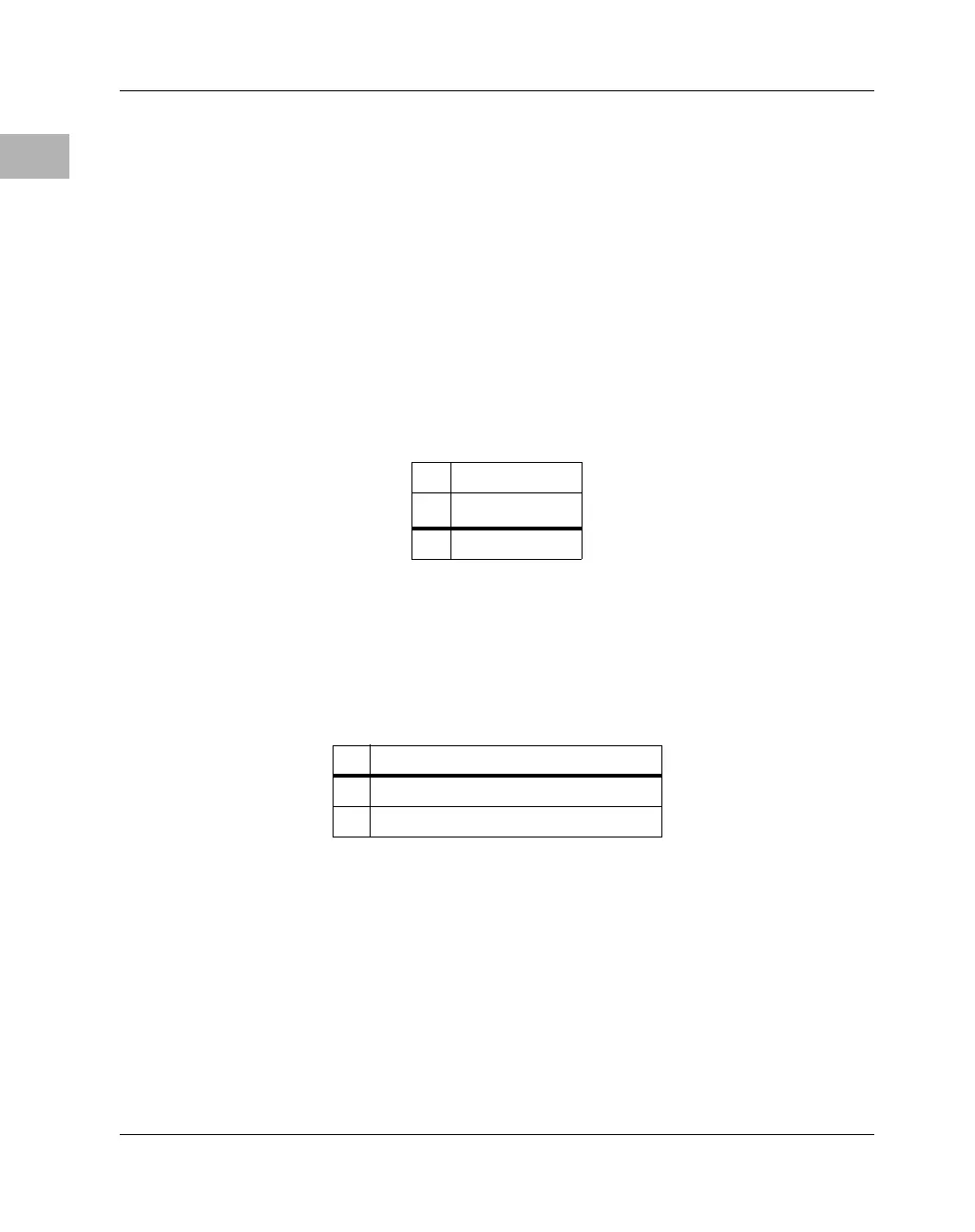

MMODE

0 Pass Through

1Mixed

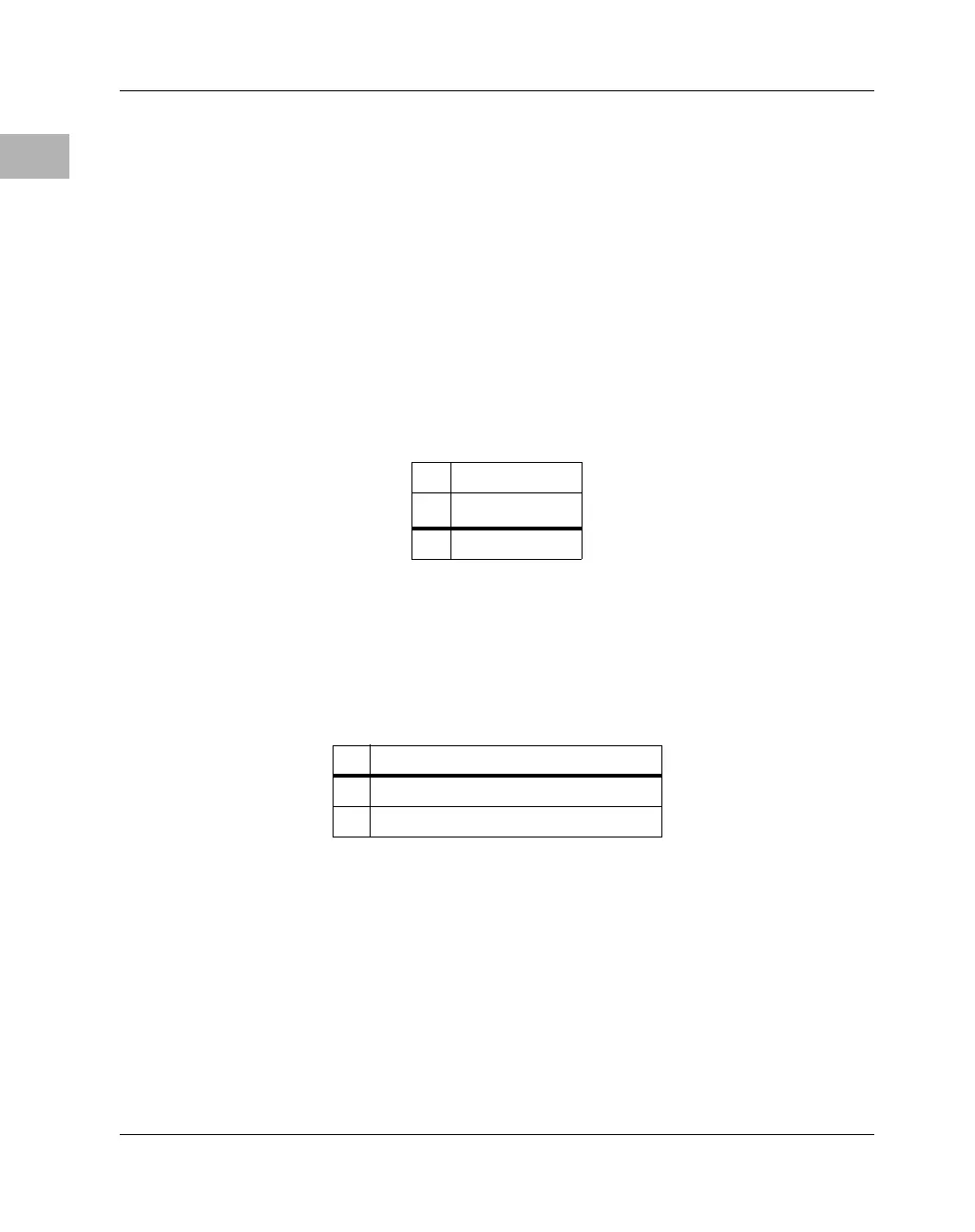

TMODE

0 Processor 0 always selected

1 Swap between Processors

Loading...

Loading...