3-52 Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

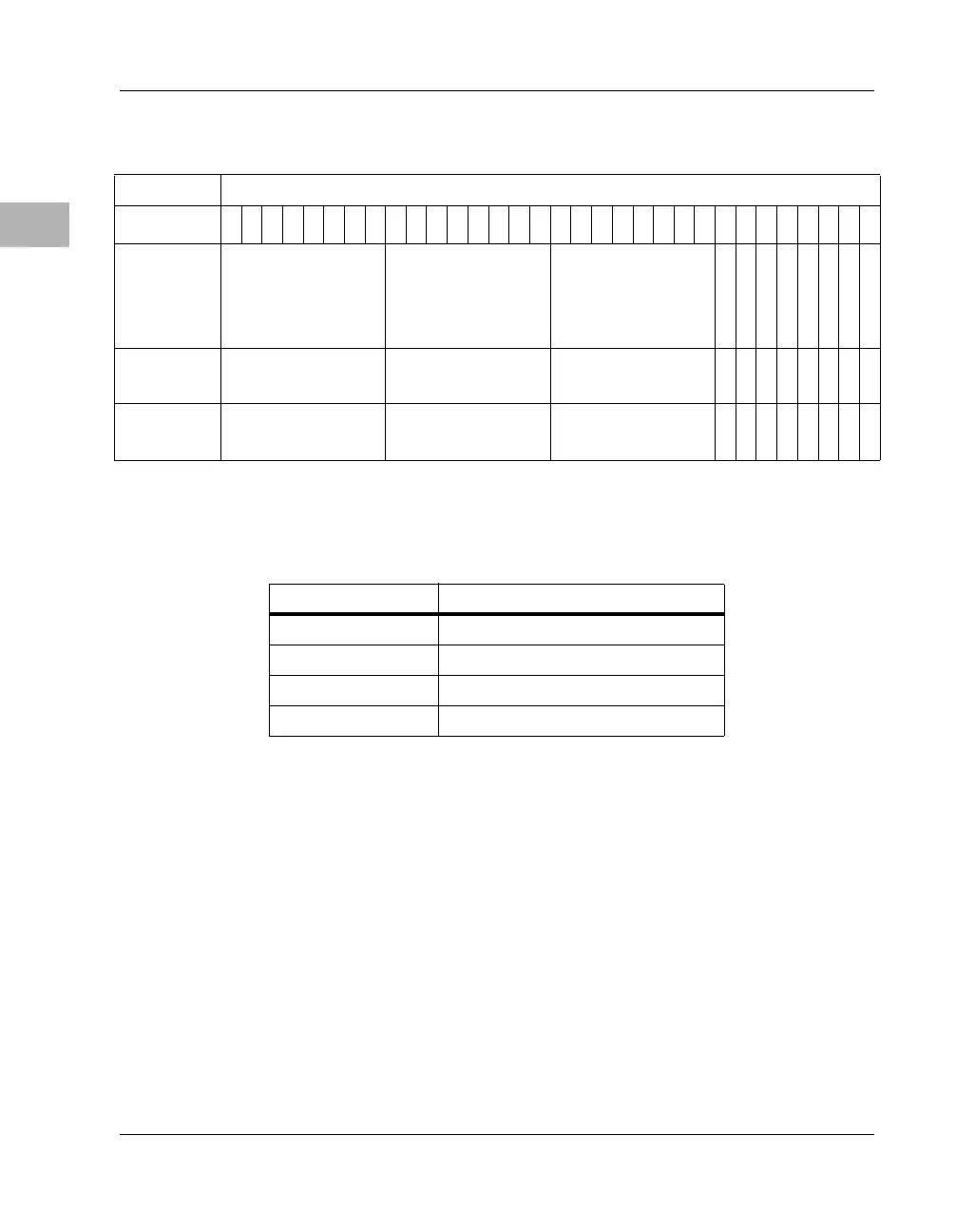

ROM Speed Control Register

rom_a_spd0,1 determine the access timing used for ROM/Flash Block A.

The encodings of these bits are as follows.

rom_b_spd0,1 determine the access timing used for ROM/Flash Block B.

See table above.

Address

$FEF80060

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

0

0

rom a spd0

rom a spd1

0

0

rom b spd0

rom b spd1

Operation

READ ZERO READ ZERO READ ZERO

R

R

R/W

R/W

R

R

R/W

R/W

Reset

XXX

X

X

0 PL

0 PL

X

X

0 PL

0 PL

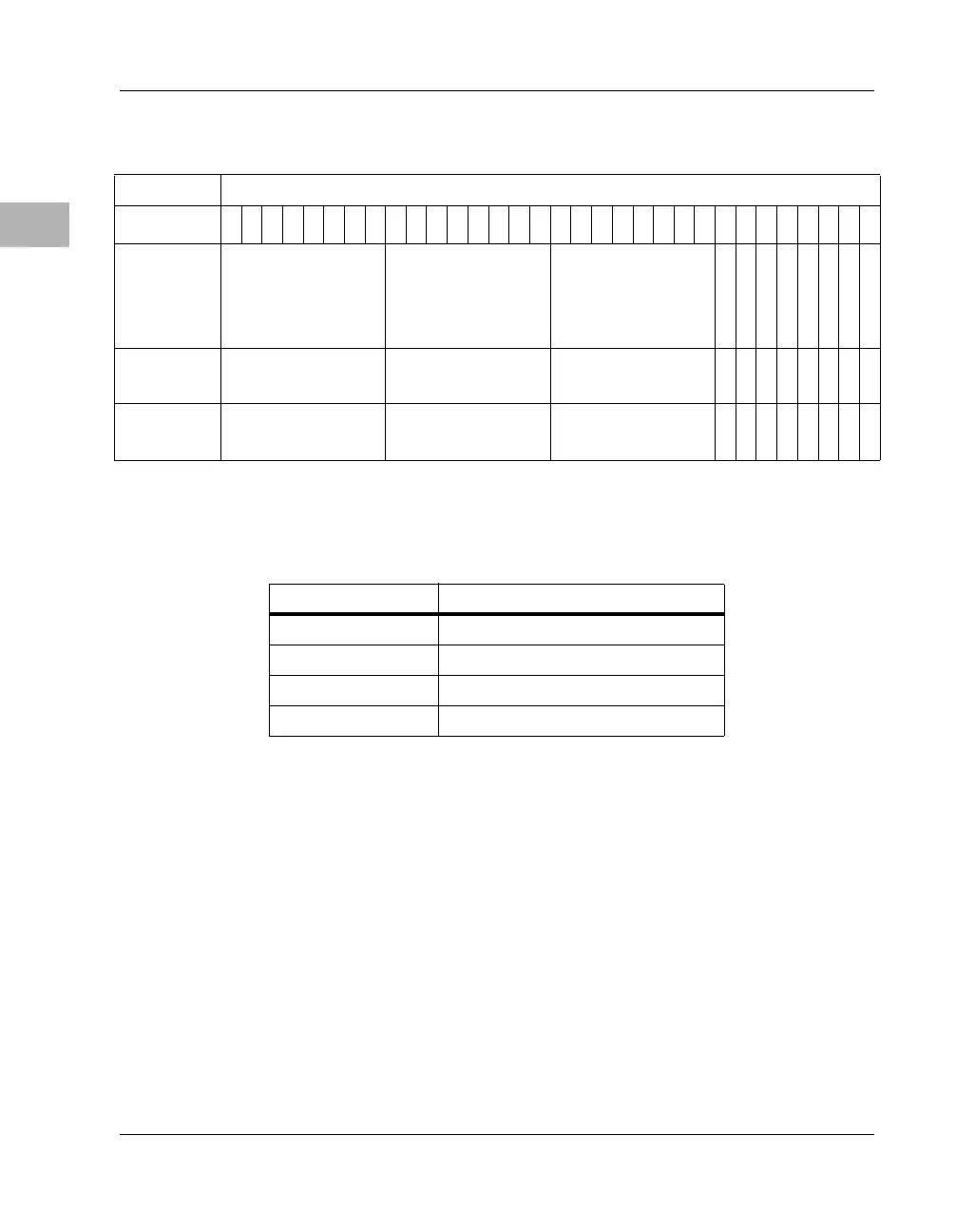

Table 3-19. Rom Speed Bit Encodings

rom_a/b_spd0,1 ROM Block A/B Access Time

%00 180ns

%01 120ns

%10 75ns

%11 45ns

Loading...

Loading...