Registers

http://www.motorola.com/computer/literature 2-25

2

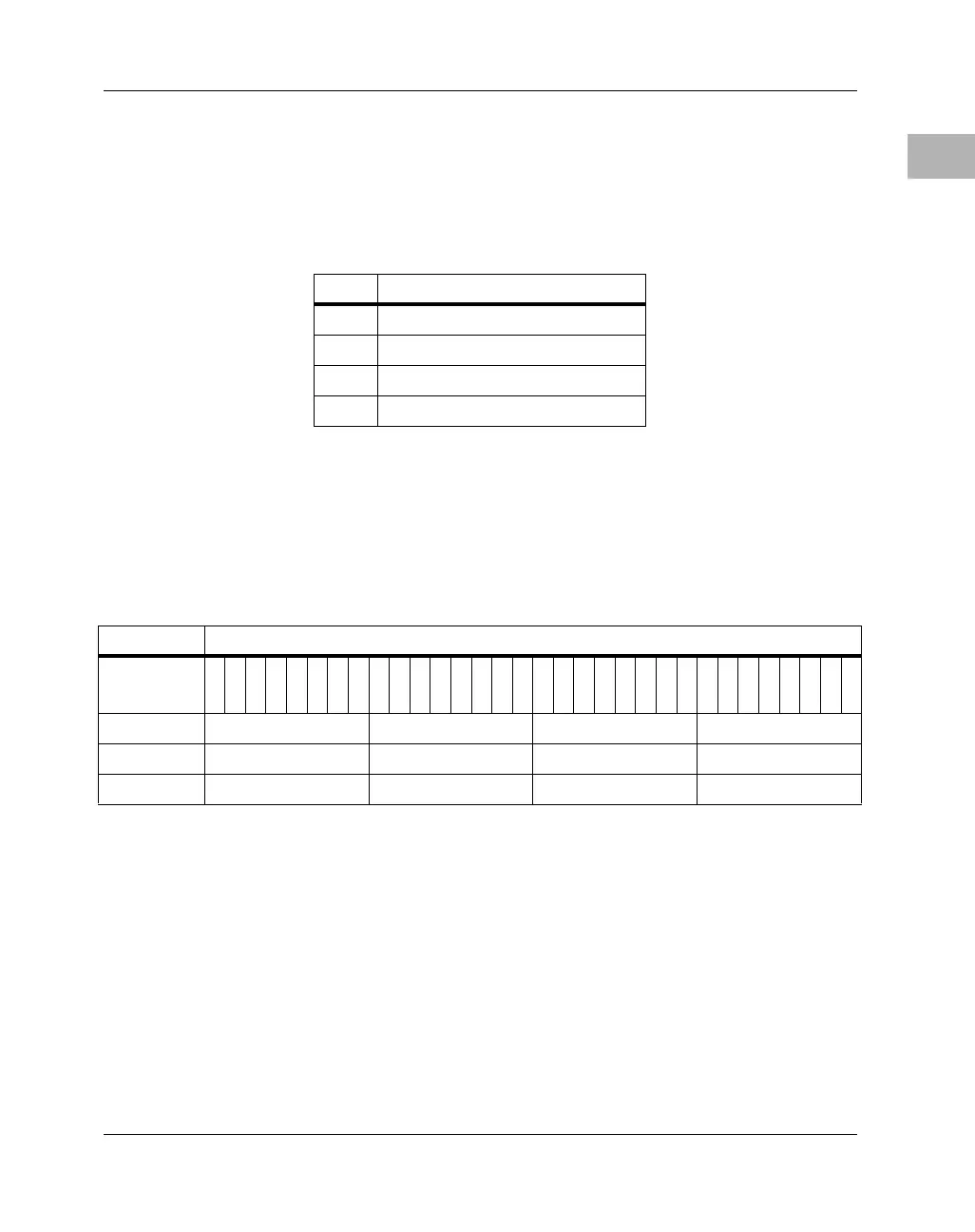

MIDx Master ID. This field is encoded as shown below to indicate who

is currently the PPC bus master. This information is obtained by sampling

the CPUID pins. In a multiprocessor environment, these bits allow

software to determine on which processor it is currently running. The

internal PPC arbiter encodes this field as follows:

FEAT Feature Register. Each bit in this register reflects the state of one

of the external interrupt input pins on the rising edge of RESET*. This

register may be used to report hardware configuration parameters to

system software.

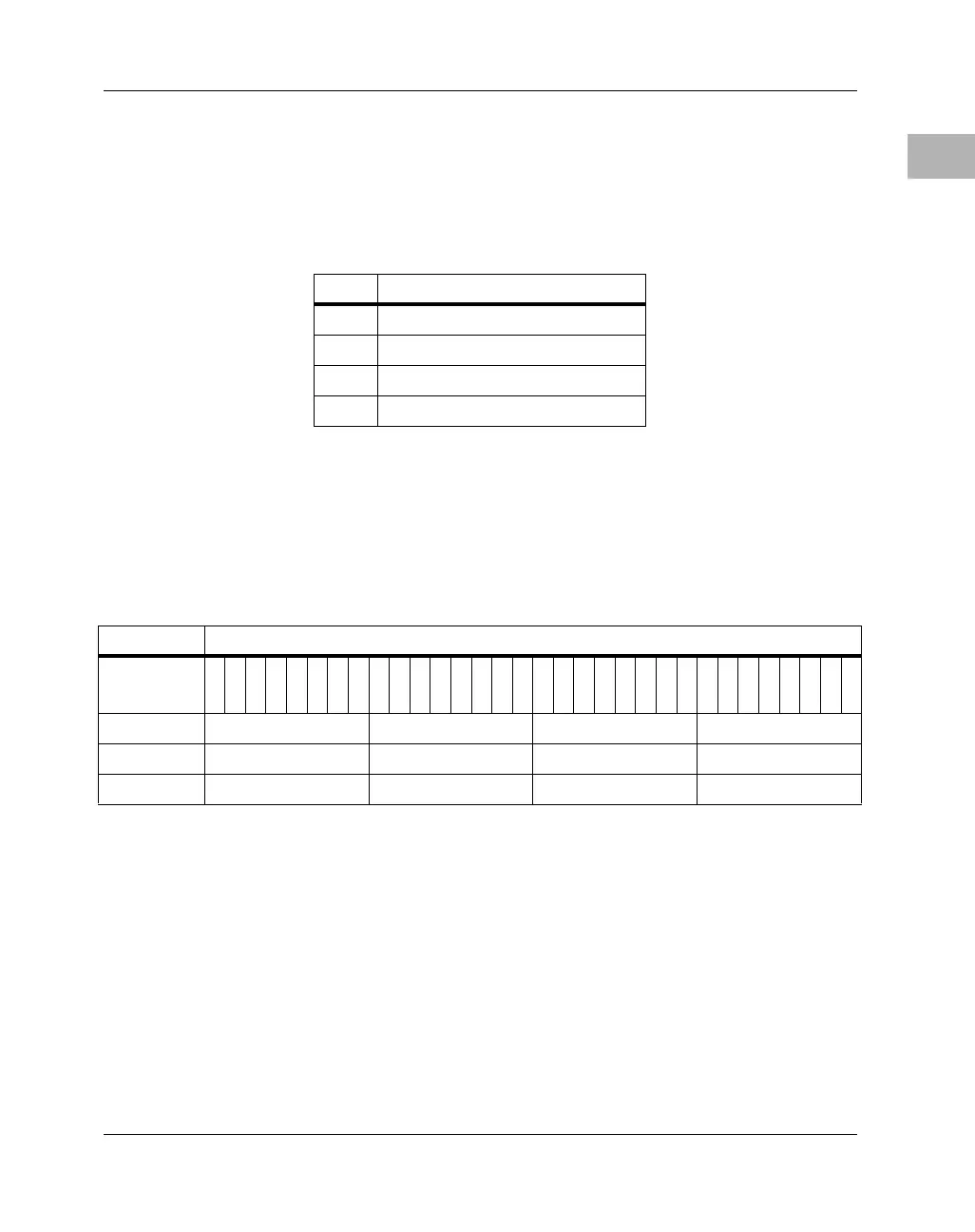

Prescaler Adjust Register

PADJ Prescaler Adjust. This register is used to specify a scale factor for

the prescaler to ensure that the time base for the bus timer is 1 MHz. The

scale factor is calculated as follows:

PADJ = 256 - Clk,

where Clk is the frequency of the CLK input in MHz. The following table

shows the scale factors for some common CLK frequencies.

MID Current PPC Data Bus Master

00 device on ABG0*

01 device on ABG1*

10 device on ABG2

11 Raven

Address $FEFF0010

Bit

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name PADJ

Operation RRRR/W

Reset $00 $00 $00 $BE

Loading...

Loading...