Registers

http://www.motorola.com/computer/literature 2-35

2

MSOFFx PPC Slave Offset. This register contains a 16-bit offset that is

added to the upper 16 bits of the PPC address to determine the PCI address

used for transfers from the PPC bus to PCI. This offset allows PCI

resources to reside at addresses that would not normally be visible from the

PPC bus.

REN Read Enable. If set, the corresponding PPC slave is enabled for read

transactions.

WEN Write Enable. If set, the corresponding PPC slave is enabled for

write transactions.

WPEN Write Post Enable. If set, write posting is enabled for the

corresponding PPC slave.

MEM PCI Memory Cycle. If set, the corresponding PPC slave will

generate transfers to or from PCI memory space. When clear, the

corresponding PPC slave will generate transfers to or from PCI I/O space

using the addressing mode defined by the IOM field.

IOM PCI I/O Mode. If set, the corresponding PPC slave will generate

PCI I/O cycles using spread addressing as defined in the section on

Generating PCI Memory and I/O Cycles. When clear, the corresponding

PPC slave will generate PCI I/O cycles using contiguous addressing. This

field only has meaning when the MEM bit is clear.

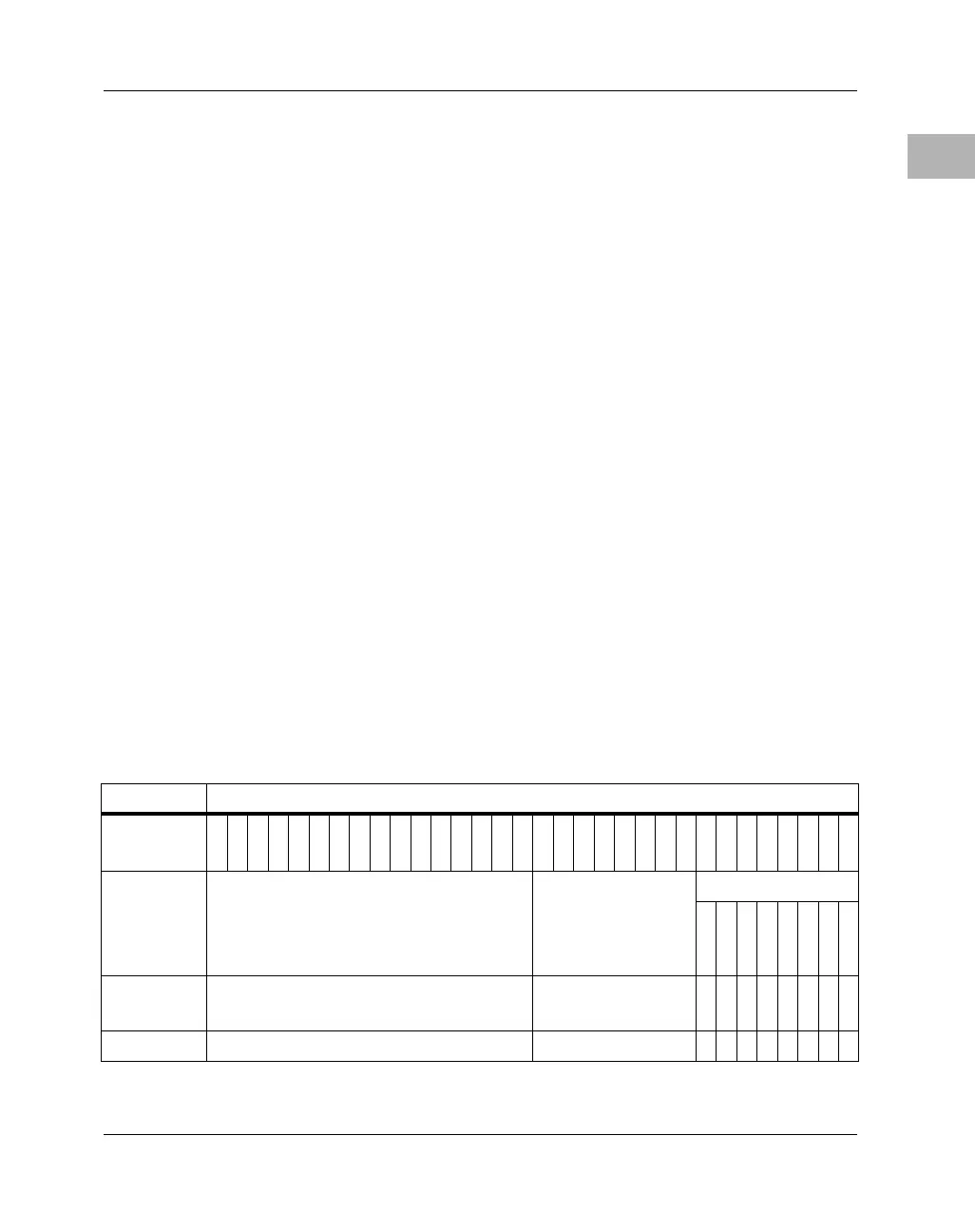

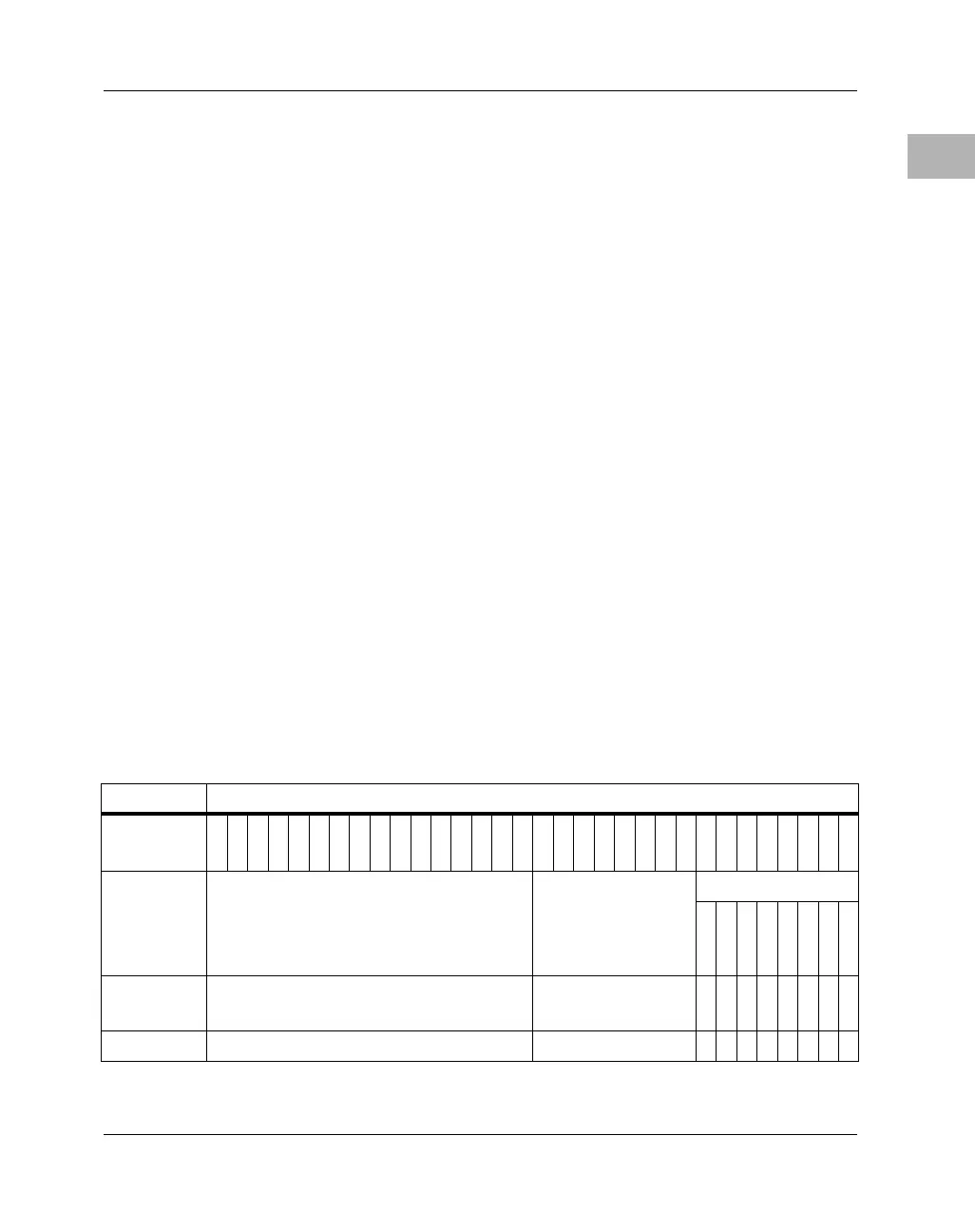

PPC Slave Offset/Attribute (3) Registers

Address MSOFF3/MSATT3 - $FEFF005C

Bit

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name MSOFF3 MSATT3

REN

WEN

WPEN

IOM

Operation R/W R

R/W

R/W

R

R/W

R

R

R

R/W

Reset $8000 $00

1

1

0

0

0

0

0

0

Loading...

Loading...