Interrupt Handling

http://www.motorola.com/computer/literature 4-7

4

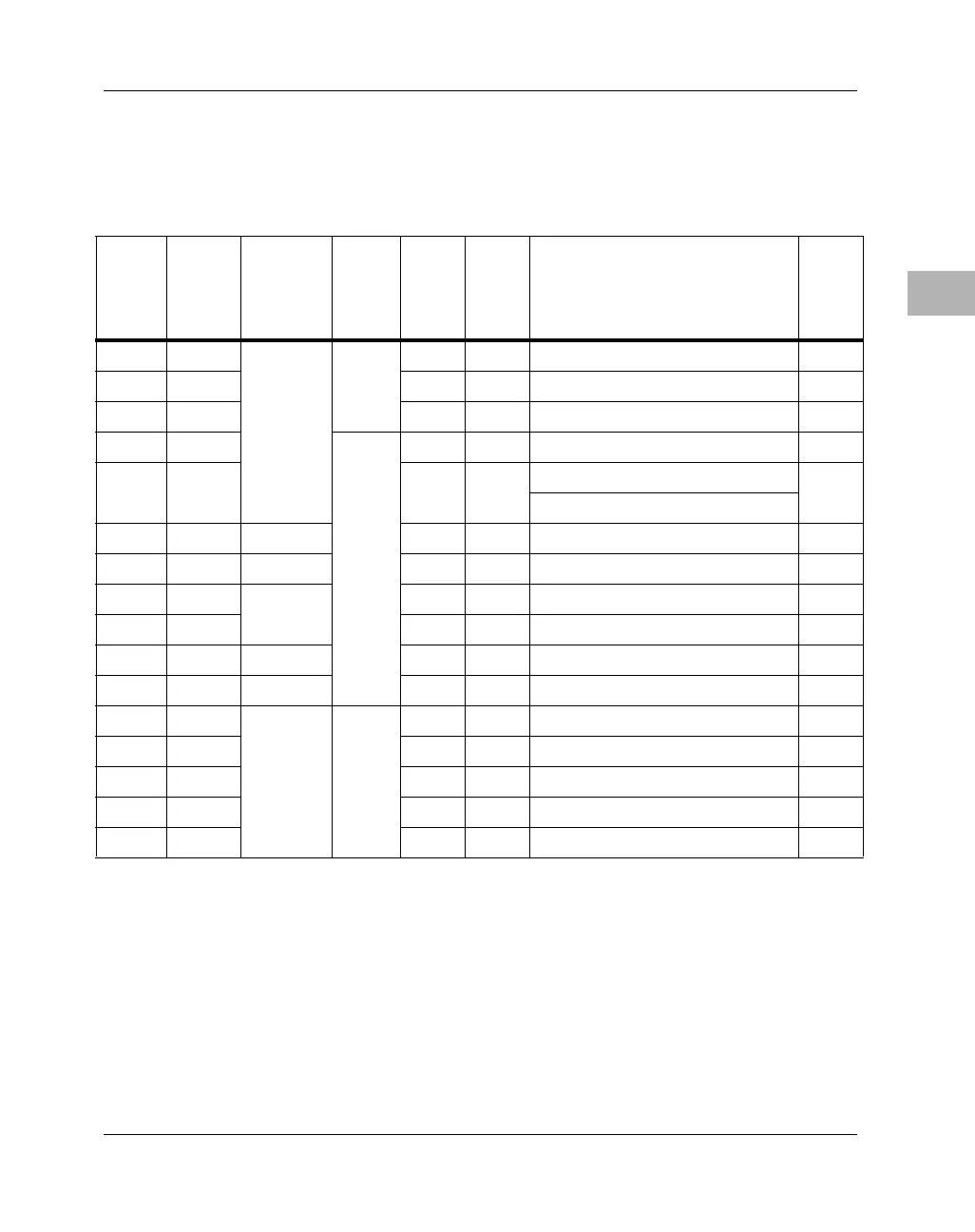

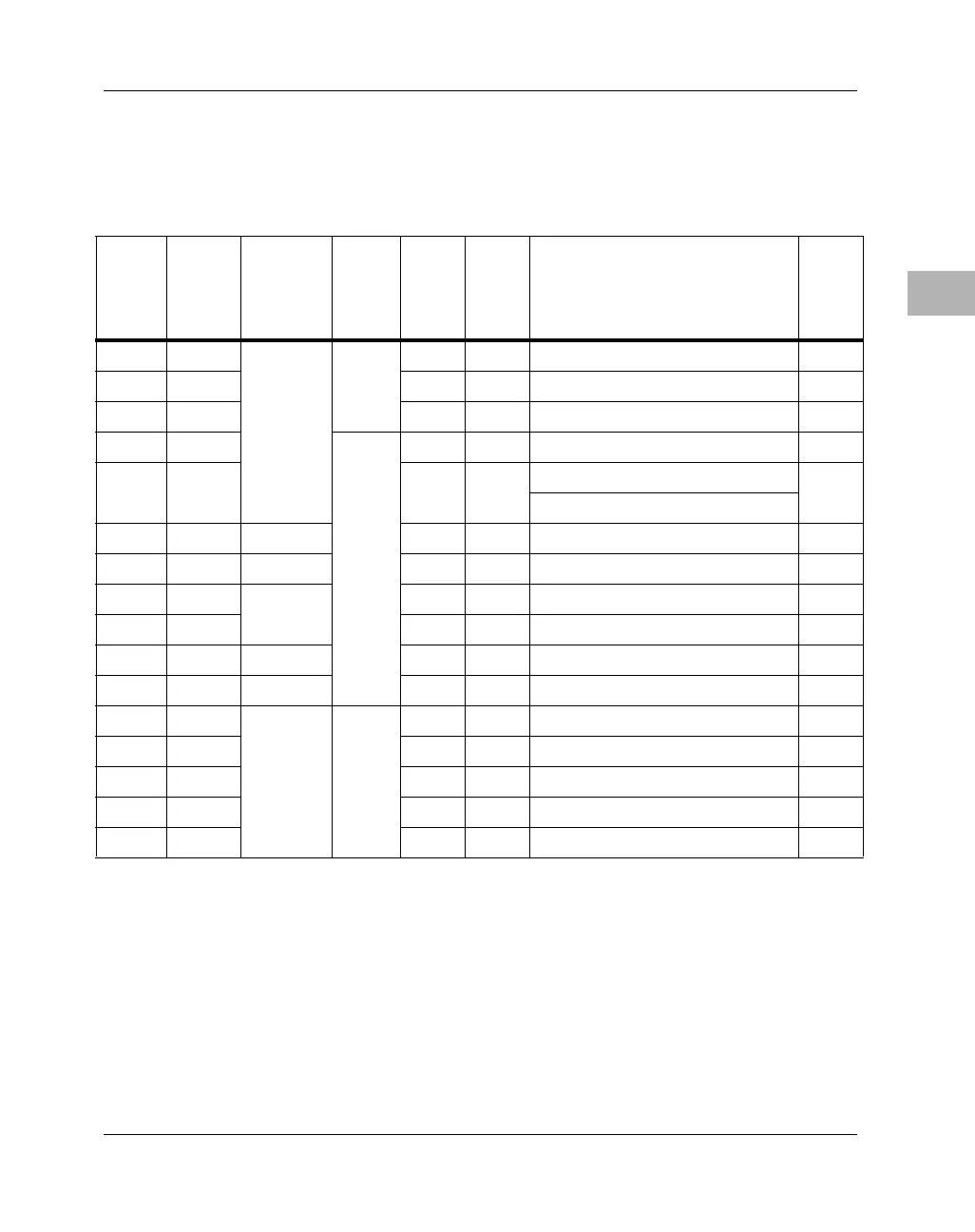

The assignments of the PCI and ISA interrupts supported by the PIB are as

follows:

Notes

1. Internally generated by the PIB.

2. Bit 4 of ISA Clock Divisor Register in the PIB must be set to 0 to

support external keyboard interrupt (from the ISASIO device).

Table 4-4. PIB PCI/ISA Interrupt Assignments

PRI ISA

IRQ

PCI

IRQ

Controller

Edge

/Leve

l

Polarity

Interrupt Source

Notes

1 IRQ0 INT1 Edge High Timer 1 / Counter 0 1

2 IRQ1 Edge High Keyboard 2

3-10 IRQ2 Edge High Cascade Interrupt from INT2

3 IRQ8_ INT2 Edge Low ABORT Switch Interrupt

4 IRQ9 Level High Z8536 CIO 3,4

Z85230 ESCC

5 IRQ10 PIRQ0_ Level Low PCI-Ethernet Interrupt 3,5,6

6IRQ11 LevelLowNot Used 6

7 IRQ12 Edge High Mouse

8 IRQ13 Edge High Not Used 6

9 IRQ14 PIRQ2_ Level Low PCI-SCSI Interrupt 3,5,6

10 IRQ15 PIRQ3_ Level Low PMC Interrupt 3,5,6

11 IRQ3 INT1 Edge High COM2 (Async Serial Port 2)

12 IRQ4 Edge High COM1 (Async Serial Port 1)

13 IRQ5 Level High Peripheral Parallel Port Interrupt

14 IRQ6 Edge High Floppy Interrupt

15 IRQ7 Edge High Host Parallel Port Interrupt

Loading...

Loading...